University of Technology الجامعة التكنولوجية

Computer Science Department قسم علوم الحاسوب Microprocessor المعالجات المايكروية

Dr. Khitam A. Salman Assist. Lecturer Mohammed Thamer Assist. Lecturer Sarab M. Taher د. ختام عبدالنبي سلمان م.م. محمد ثامر

cs.uotechnology.edu.iq

# Microprocessors – 1'st course (Syllabus)

- Introduction to Microprocessor and Microcomputer system.

- Microprocessor Architecture and Register Set.

- System Buses

- Memory types and physical addressing.

- I/O devices

- Instruction Set and Format

- Addressing Modes

- Introduction to Assembly Programming Language.

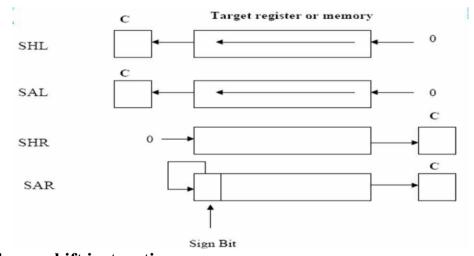

- Arithmetic and logical Instructions (Shift and Rotate).

- Program Control (interrupt and subroutine call).

#### **References:**

- **1.** Abel P., "IBM PC Assembly Language and Programming", 4<sup>th</sup> Edition, Prentice Hall, 1998..

- Thorne M., "Computer Organization and Assembly Language Programming", 2<sup>nd</sup> Edition, Benjamin/Cummings, 1990.

#### **Introduction to Microprocessors**

#### **Electronic and Logic Circuits**

Modern devices contain two types of circuits:

#### **Electronic circuits**

The basic components of electronic circuits are transistors, resistors, capacitors, etc. Electronic circuits operate on a wide range of voltages such as (1V, 2.1V, 3.3V, 12V) positive or negative and deal with analog signals.

#### **Logic Circuits**

The basic component of digital circuits are logic gates such as AND, OR, NAND, NOR, XOR, XNOR, NOT... which deal with digital signals.

# **Integrated Circuits (IC)**

Integrated circuits consist of logic and electronic circuits built on a single small block or chip of semiconductor that all work together to perform a specific task. The IC is easily breakable, so to be attached to a circuit board, it is often housed in a plastic package with metal pins.

Figure 1 Integrated circuits of Microprocessor

#### Microprocessor

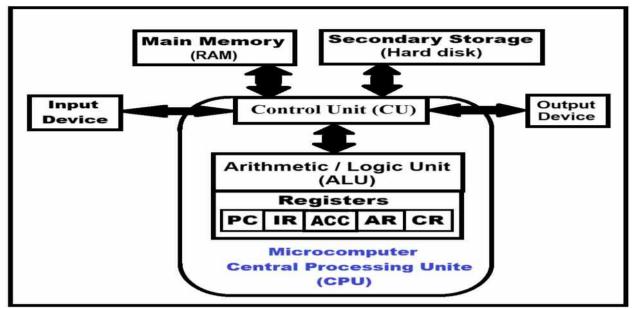

Computer's Central Processing Unit (CPU) built on a single Integrated Circuit (IC) is called a microprocessor. A digital computer with one microprocessor which acts as a CPU is called microcomputer. It is a programmable, multipurpose, clock-driven, register-based electronic device that reads binary instructions from a storage device called memory, accepts binary data as input and processes data according to those instructions and provides results as output.

Figure 2 Main Component of Microprocessor

# Central processing unit (CPU)

The CPU supervises and controls all other computer units, transfers data to and from these units, and performs the arithmetic and logical operations necessary to transform data into meaningful information. It called "Processor" or "Microprocessor" in personal computer. It is divided into three parts:

- 1- Arithmetic and Logic unit (ALU).

- 2- Control unit (CU).

- 3- Register.

# 1. Arithmetic and Logic unit (ALU).

Perform the processing of data including arithmetic operations such as addition, subtraction, multiplication, division and logic operations including comparison (ex. A<B) and sorting.

# 2. Control Unit (CU).

The control unit coordinates the operation of the entire computer system automatically, and acts as a central nervous system that sends control signals to other computer units. The operations it performs are:

- 1- Control of input and output devices.

- 2- Sending and retrieving information to and from memory's (primary and secondary memory).

- 3- Routing of information between the main memory (RAM) and the arithmetic and logic unit (ALU).

- 4- Direct and coordinates all units of the computer to execute program steps.

# 3. Registers

Registers are a type of computer memory used to quickly accept, store, and transfer data and instructions that are being used immediately by the CPU. The most important registers are:

- 1- Instruction Register (IR): It contains the instruction being executed.

- 2- Program Counter Register (PC): It contains the address of the next instruction to be executed.

- 3- Address Register (AR): holds the address of memory location.

- 4- Data Register (DR): Holds data that is being transferred to or from memory.

- 5- Accumulator Register (ACC): Where intermediate arithmetic and logic results are stored.

# The basic operations performed by microprocessor

A microprocessor does three basic things.

- 1- Using its ALU to perform arithmetic and logical operations. Modern microprocessors contain complete floating-point processors that can perform extremely sophisticated operations on large floating-point numbers.

- 2- A microprocessor can move data from one memory location to another.

- 3- A microprocessor can make decisions and jump to a new set of instructions based on those decisions.

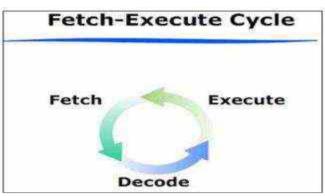

# **Instructions Fetch-Execute Cycle**

The microprocessor follows the following sequence to execute instructions.

- 1. Initially: the microprocessor loads the program instructions into main memory.

- 2. Fetch: The microprocessor fetches those instructions from the memory.

- 3. **Decode:** Separate the operation from the operands and replace the variables with their real values stored in main memory in preparation for execution.

- 4. **Execute:** Executes these instructions until the end of the program (until all instructions are performed).

- 5. Later: it sends the result in binary to the output device.

Between these processes the register stores the temporarily data and ALU performs the computing functions.

Figure 3 Sequence of Execute Instructions Cycle

#### **<u>Q: How does the CPU Fetch and execute program instructions?</u>**

- 1. Fetch: Fetch the instruction from memory to IR.

- 2. Change the address of Program Counter PC to the next instruction.

- 3. **Decode**: Determine the type of the instruction to be execute.

- If the instruction uses data in memory, use the address in the AR register to fetch the data.

- Fetch the data into DR register (Data Register).

- 4. **Execute:** Execute the instruction.

- 5. Store the result in the ACC register or in a proper place or send it to the output device.

- 6. Go to step 1 to Fetch the next instruction whose address in PC register.

#### List of Terms Used in a Microprocessor

Here is a list of some of the used terms in a microprocessor.

- <u>Instruction Set:</u> It is the set of instructions that the microprocessor can understand (Ex: MOV, ADD, SUB...). The instruction set acts as an interface between the software and hardware.

- <u>Bus:</u> The bus is used for the transmission of data, address and control information. This transmission occurs in different elements of the microprocessor. The bus in this is basically of three types which are **data bus**, address bus and control bus.

This microprocessor has:

$\checkmark$  A data bus (that may be 8, 16, 32 or 64 bits wide) that can send data to memory or receive data from memory.

$\checkmark$  An address bus (that may be 8, 16, 32 or 64 bits wide) that sends an address to memory.

$\checkmark$ An RD (read) and WR (write) line to tell the memory whether it should set or get the addressed location.

$\checkmark$  A clock line that lets a clock pulse sequence the processor

$\checkmark$  A reset line that resets the program counter to zero (or whatever) and restarts execution

• <u>Word Length</u>: It depends upon the (number of bits) of internal data bus, registers, ALU, etc. A 16-bit microprocessor can process 16-bit data at a time. The word length ranges from 4 bits to 64 bits depending on the type of the microcomputer. A processor with longer word length is more powerful and can process data at a faster speed as compared to a processor with shorter word length.

NOT: The power of the given microprocessor is measured in terms of bits.

- <u>Clock Speed:</u> It determines the number of operations per second the processor can perform. It is expressed in megahertz (MHz) or gigahertz (GHz). It is also known as Clock Rate.

- **<u>Data Types:</u>** The microprocessor has multiple data type formats like Decimal, Hexadecimal, Binary, signed and unsigned numbers.

#### **Evolution of Microprocessors (**

We can categorize the microprocessor according to the generations or according to the size of the microprocessor. The following table shows this categorization.

| Generation                 | Year      | Size   | Example      | Features                           |

|----------------------------|-----------|--------|--------------|------------------------------------|

| 1 <sup>st</sup> generation | 1971-1972 | 4 bits | 4004         | Basic operation and it has limited |

|                            |           |        |              | memory and the control unit        |

|                            |           |        |              | executes fetch, decode and         |

|                            |           |        |              | execute instructions               |

| 2 <sup>nd</sup> generation | 1973      | 8 bits | Intel 8008 & | Improved processing speed,         |

| -                          |           |        | 8080         | better instruction sets            |

| Tabl | e | 1 | Evolu | tion | of | Micro | process | or |

|------|---|---|-------|------|----|-------|---------|----|

|      |   |   |       |      |    |       |         |    |

| Generation                 | Year      | Size    | Example           | Features                      |

|----------------------------|-----------|---------|-------------------|-------------------------------|

| 3 <sup>rd</sup> generation | 1978      | 16 bits | Intel 8086, Zilog | Its performance like          |

|                            |           |         | Z800 and 80286    | minicomputers. Enhanced       |

|                            |           |         |                   | memory access, pipelining     |

|                            |           |         |                   | introduced                    |

| 4 <sup>th</sup> generation | 1985-1994 | 32 bits | Intel 80386,      | Integrated FPU, cache memory, |

|                            |           |         | 80486, Motorola   | faster processing             |

|                            |           |         | 68020             |                               |

| 5 <sup>th</sup> generation | 195-2005  | 64 bits | Intel Pentium,    | Super scalar architecture,    |

|                            |           |         | AMD Athlon,       | advanced power management     |

|                            |           |         | PowerPC G4        |                               |

| 6 <sup>th</sup> generation | 2006 up   | Multi-  | Intel Core        | Multi-core processing, AI     |

|                            | now       | core    | i3/i5/i7/i9,      | acceleration, high energy     |

|                            |           |         | AMD Ryzen,        | efficiency                    |

|                            |           |         | Apple M-series    |                               |

# **Introduction to Microcomputers**

*Microcomputer* is a digital computer with one microprocessor which acts as a CPU.

*Microcomputer*: small computers, also called personal computers (PC), can fit next to a desk or on a desktop, or can be carried around. They are either standalone machines or are connected to a computer network such as a local area network *LAN*. LAN connects, usually by special cable, a group of desktop PCs and other devices, such as printers, in an office or a building.

Computers used nowadays can be known as general purpose machines or special purpose machines.

*General purpose machines* are machines that built with no specific application in mind, but rather are capable of performing computation needed by different applications.

Special purpose machines: are machines that to serve specific applications.

- 1. *Desktop PCs*: are those in which the case or main housing sits on a desk, with keyboard in front and monitor (screen) often on top.

- 2. *Tower PCs*: are those Microcomputer in which the case sits as a "tower," often on the floor beside a desk, thus freeing up desk surface space.

- 3. *Laptop computers (notebook computers):* are lightweight portable computers with built-in monitor, keyboard, hard-disk drive, battery, and AC adapter that can be plugged into an electrical outlet; their weight anywhere from 1.8 to 9 pounds.

- 4. *Personal digital assistants (PDAs)* (handheld computers or palmtops) combine personal organization tools-schedule planners, address books, todo lists. Some are able to send e-mail and faxes. Some PDAs have touchsensitive screens. Some also connect to desktop computers for sending or receiving information.

- 5. *Microcontrollers (tiny computers*: Microcontrollers, also called embedded computers, are the tiny, specialized microprocessors installed in "smart" appliances and automobiles. These microcontrollers enable PDAs, microwave ovens, for example to store data about how long to cook your potatoes and at what temperature.

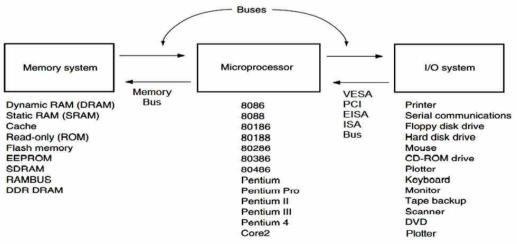

#### The Microprocessor-Based Personal Computer System

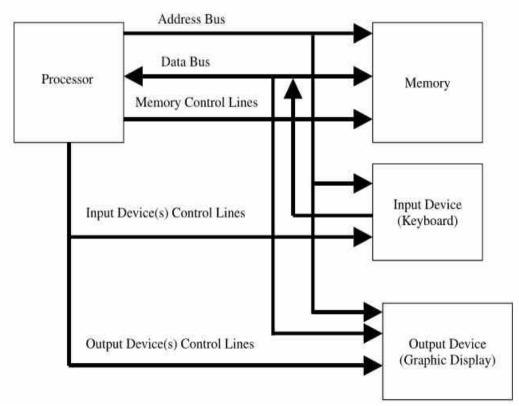

Machines that once filled large areas have been reduced to small desktop computer systems. Companies such as DEC (Digital Equipment Corporation now owned by Hewlett-Packard Company) have stopped producing mainframe computer systems in order to concentrate their resources on microprocessor-based computer systems. PC consists of three main blocks which are: microprocessor, memory system and I/O systems. These blocks are interconnected by buses. A bus is a set of common connections that carry the same type of information. Figure 4 shows the general block diagram of the microcomputer

# Memory system

Memory unit in microprocessor is used to store information such as numbers, characters and so on. Storing information means that the memory has the ability to hold this information for processing or for later use. Programs that define how the computer work are also stored in the memory.

Memory can be divided into: *primary storge* that is used for temporary storage and it is normally of small size and *secondary storage* which is used for long term storage.

The primary storage is further divided into *Read Only Memory (ROM)* and *Random Access Memory (RAM)*. The information stored in ROM are nonvolatile, that is the information is not lost when the power turned off. On the other hand, the information stored in RAM are volatile can be modified.

# **Input/Output System**

The microcomputer system contains input and output (I/O) devices that allow the system to communicate with the external environment. Keyboard, mouse, joystick and microphone are examples of the input devices. On the other hand the most used output devices are printers, displays and speakers.

# **Performance measure**

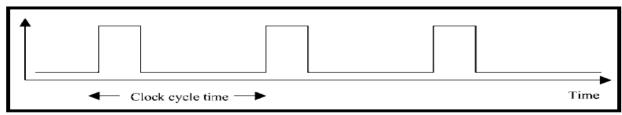

The clock synchronizes the internal operations of the CPU with other components in the system. CPU speed is determined by a clock cycle, which is the time between two rising edges of a periodic clock signal. Figure 5 shows the clock cycle time

Figure 5 Clock signal

The higher number of pulses per second, the faster the processor. The clock speed is measured in Hz, often either MHz (megahertz) or GHz (gigahertz). For example, a 4 GHz processor performs 4,000,000,000 clock cycles per second.

**Instructions Per Cycle (IPC):** it measures how many instructions a CPU is capable of executing in a single clock. The performance of a processor can be measured by calculating the average number of *Clock cycles Per Instruction (CPI)*.

The instruction set of a given machine consists of a number of instruction categories: *ALU* (simple assignment and arithmetic and logic instructions), *load and store, branch* and others In case that CPI for each instruction category is known then the overall CPI can be computed as:

$$CPI = \frac{\sum_{i=1}^{n} CPI_i \times I_i}{Instruction \ count}$$

Where  $I_i$  is the number of times an instruction of type i is executed in the program and  $CPI_i$  is the average number of clock cycles needed to execute such instruction.

#### **Example:**

Use the CPI to measure the performance of a computer, which records the following metrics in table 2when you run a set of benchmarking programs.

| Instruction Category | Percentage of occurrence | No. of cycles per instruction |

|----------------------|--------------------------|-------------------------------|

| ALU                  | 38                       | 1                             |

| Load & store         | 15                       | 3                             |

| Branch               | 42                       | 4                             |

| Others               | 5                        | 5                             |

#### **Solution:**

$$CPI = \frac{\sum_{i=1}^{n} CPI_{i} \times I_{i}}{Instruction \ count}$$

Instruction count = 38+15+42+5 =100

$$CPI = \frac{38 \times 1 + 15 \times 3 + 42 \times 4 + 5 \times 5}{100} = 2.76$$

#### Million Instructions-Per-Second (MIPS)

MIPS is a measure of a processor's speed, providing a standard for representing the number of instructions that a CPU can process in one second. The number is meant to indicate how well a computer performs and how much work it can do.

$$MIPS = \frac{clock \ rate}{CPI \ \times \ 10^6}$$

#### Example:

Use MIPS to measure the performance of a computer for which the following metrics are recorded when running a set of benchmarking programs in table3. Assume that the clock rate of the CPU is 200 MHz

| Instruction Category | Table 3 Machine informationPercentage of occurrence | No. of cycles per instruction |

|----------------------|-----------------------------------------------------|-------------------------------|

| ALU                  | 35                                                  | 1                             |

| Load & store         | 30                                                  | 2                             |

| Branch               | 15                                                  | 3                             |

| Others               | 20                                                  | 5                             |

#### Solution:

$$CPI = \frac{\sum_{i=1}^{n} CPI_i \times I_i}{Instruction \ count}$$

**Instruction count** = 35+30+15+20 =100

$$CPI = \frac{35 \times 1 + 30 \times 2 + 15 \times 3 + 20 \times 5}{100} = 2.4$$

$$MIPS = \frac{clock \ rate}{CPI \ \times \ 10^6}$$

$$MIPS = \frac{200 \ MHz}{2.4 \ \times \ 10^6}$$

#### **Note:**1 MHz = 1 000 000 hertz = 10<sup>6</sup> hertz

$$MIPS = \frac{200 \, M \times 10^6}{2.4 \times 10^6} = 83.67$$

The MIPS scale can be used to compare computers and determine which one has better performance. For example, a computer that can process 12,000 MIPS should be able to outperform one that processes 10,000 MIPS.

#### Example3:

What is the MIPS for the devices (A, B) shown in table 4? assuming the clock rate is 200 MHz

|                         | Machine A                      |                                     | Machine B               |                                |                                     |

|-------------------------|--------------------------------|-------------------------------------|-------------------------|--------------------------------|-------------------------------------|

| Instruction<br>Category | Percentage<br>of<br>occurrence | No. of cycles<br>per<br>instruction | Instruction<br>Category | Percentage<br>of<br>occurrence | No. of cycles<br>per<br>instruction |

| ALU                     | 38                             | 1                                   | ALU                     | 35                             | 1                                   |

| Load &<br>store         | 15                             | 3                                   | Load & store            | 30                             | 2                                   |

| Branch                  | 42                             | 4                                   | Branch                  | 15                             | 3                                   |

| Others                  | 5                              | 5                                   | Others                  | 20                             | 5                                   |

Table 4 Machine A and B information

Solution:

$$CPI_a = \frac{\sum_{i=1}^{n} CPI_i \times I_i}{Instruction \ count} = \frac{38 \times 1 + 15 \times 3 + 42 \times 4 + 5 \times 5}{100} = 2.76$$

$$MIPS_{a} = \frac{clock \ rate}{CPI \times 10^{6}} = \frac{200 \times 10^{6}}{2.76 \times 10^{6}} = 70.24$$

$$CPI_{b} = \frac{\sum_{i=1}^{n} CPI_{i} \times I_{i}}{Instruction \ count} = \frac{35 \times 1 + 30 \times 2 + 15 \times 3 + 20 \times 5}{100} = 2.4$$

$$MIPS_{b} = \frac{clock \ rate}{CPI \times 10^{6}} = \frac{200 \times 10^{6}}{2.4 \times 10^{6}} = 83.67 =$$

$$MIPS_{b}(83.67) > MIPS_{a}(70.24)$$

Thus: M  $PS_b(83.67) > MIPS_a(70.24)$

#### **Microprocessor Architecture**

8086 Microprocessor is an enhanced version of 8085 Microprocessor that was designed by Intel in 1976. This 16 Bit Microprocessor have 20-bit address lines and16-bit data lines that provides up to 1MB storage. It consists of powerful instruction set, which provides operations like multiplication and division easily. It supports two modes of operation *Maximum mode and Minimum mode*. Maximum mode is suitable for system having multiple processors and Minimum mode is suitable for system having a single processor.

#### **Features of 8086 Microprocessors**

The most prominent features of an 8086 microprocessor are as follows:

- It is a 16-bit Microprocessor. Its ALU, internal registers work within 16bit binary word.

- It has a 20-bit address bus which can access up to  $2^{20} = 1 MB$  memory locations.

- It has 16-bit data bus. It can read or write to a memory/port 16 bits or bit at a time.

- It provides 14,16-bit registers.

- The frequency range of the 8886 microprocessor is 6-10 Hz.

- It has multiplexed address bus and data bus  $D_0-D_{15}$  and  $A_{17}-A_{19}$

- It has an instruction queue, which is capable of storing six instruction bytes from the memory resulting in faster processing.

- It can prefetch up to 6 instruction bytes from memory and queues them in order to speed up the instruction execution.

- It requires +5V power supply.

#### Comparison between 8085 & 8086 Microprocessor

- Size 8085 is 8-bit microprocessor, whereas 8086 is 16-bit microprocessor.

- Address Bus 8085 has 16-bit address bus while 8086 has 20-bit address bus.

- Memory 8085 can access up to 64Kb, whereas 8086 can access up to 1 Mb of memory.

- Instruction 8085 doesn't have an instruction queue, whereas 8086 has an instruction queue.

- **Pipelining** 8085 doesn't support a pipelined architecture while 8086 supports a pipelined architecture.

- I/O 8085 can address 2<sup>8</sup> = 256 I/O's, whereas 8086 can access 2<sup>16</sup> = 65,536 I/O's.

- Cost The cost of 8085 is low whereas that of 8086 is high.

- **Operation mode**: 8085 has single operation mode while 8086 has *minimum mode* which suits systems that have one processor and maximum mode that suits for multiprocessors systems

#### **Microprocessor 8086 Architecture**

The internal architecture of 8086 family of microprocessor has changed from the original 8086 to the 80386. All members of 8086 family employ the parallel processing. That is, they are implemented with several simultaneously operating processing units. Each unit has a dedicated function and they operate at the same time. The more parallel processing the higher microprocessor performance.

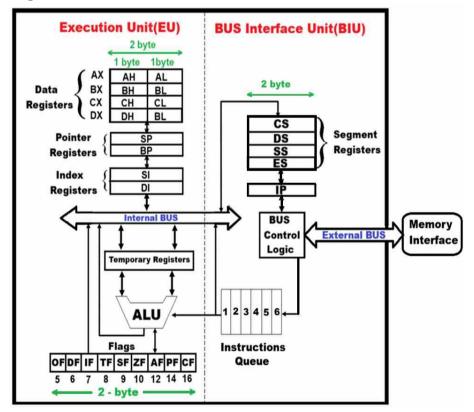

8086 microprocessors contain two processing units: the *Bus Interface Unit* (*BIU*) *and the Execution Unit (EU*). Figure (6) depicts the architecture diagram of the microprocessor 8086.

Figure 6 Microprocessor 8086 Architecture

# **Bus Interface Unit (BIU)**

It provides a full 16-bit bidirectional data bus and 20-bit address bus. This unit fetches a set of program instructions from main memory and queuing them in an instruction queue to be executed later by the execution unit. This unit acts as a control unit that is connected to the *memory and external computer parts* via the *external bus* and is connected to the *Execution Unit (EU) via the internal bus*. It is responsible for transmitting data, addresses and control signals on these buses. BIU performs the following operations:

- 1- Fetches instruction from main memory.

- 2- Supports instruction queuing.

- 3- Sends address of the memory or I/O.

- 4- Reads data from port/memory.

- 5- Writes data into port/memory.

The BIU uses a mechanism known as *instruction stream queue* to implement pipeline architecture. The *Instruction queue*, as mentioned before can store up to 6-byte instruction to be executed by the EU. When the EU execute the current instruction, the next instruction to be executed will be ready in the instruction queue. This lead to increase the execution speed.

# **Execution Unit (EU)**

The execution unit is responsible for decoding and executing all instructions. It consists of: *ALU*, *status and control flag, general-purpose registers and temporary registers*.

The EU extract the instruction from the top of the instruction queue in the BIU, decode them, generates operands, if necessary, passes them to the BIU and requests it to perform the read or write by cycles to memory or to I/O and perform the operation specified by the instruction on the operands.

During the execution of the instruction, the EU tests the status and control flags and updates them based on the result of executing the instruction.

# **Microprocessor 8086 - Pin Configuration**

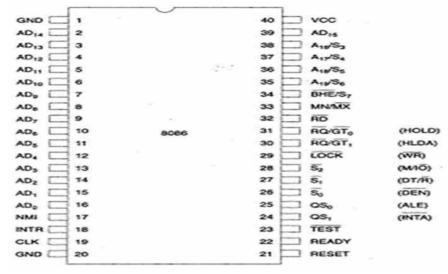

8086 was the first 16-bit microprocessor available in 40-pin Dual Inline Package (DIP) chip. Let us now discuss in detail the pin configuration of an 8086 Microprocessor.

#### 8086 Pin Diagram

The pin diagram of 8086 microprocessors is shown in Figure 7. Some of these signals are explained as follows

Figure 7 8086 Pin Diagram

- 1. **MN/MX':** It stands for *Minimum/Maximum* and is available at pin 33. It indicates what mode the processor is to operate in; when it is high, it works in the minimum mode and vice-averse. 8086 supports two modes of operation Maximum mode and Minimum mode. Maximum mode is suitable for system having multiple processors and Minimum mode is suitable for system having a single processor.

- Address/data bus: AD0-AD15. These are 16 address/data bus. AD0-AD7 carries low order byte data and AD8-AD15 carries higher order byte data. During the first clock cycle, it carries 16-bit address and after that it carries 16-bit data.

- 3. Address/status bus: A16-A19/S3-S6. These are the 4 address/status buses. During the first clock cycle, it carries 4-bit address and later it carries status signals.

- 4. **Read** (**RD**): It is available at pin 32 and is used to read signal for Read operation.

- 5. **Ready**: It is available at pin 22. It is an acknowledgement signal from I/O devices that data is transferred. It is an active high signal. When it is high, it indicates that the device is ready to transfer data. When it is low, it indicates wait state.

- 6. **RESET:** It is available at pin 21 and is used to restart the execution. It causes the processor to immediately terminate its present activity. This signal is active high for the first 4 clock cycles to RESET the microprocessor.

- 7. **M/IO**: This signal is used to distinguish between *memory and I/O operations*. When it is high, it indicates I/O operation and when it is low indicating the memory operation. It is available at pin 28.

- 8. **WR:** It stands for *write signal* and is available at pin 29. It is used to write the data into the memory or the output device depending on the status of M/IO signal.

- 9.  $QS_1$  and  $QS_0$ : These are queue status signals and are available at pin 24 and 25. These signals provide the status of **instruction queue**. Their conditions are shown in the following table

| QS <sub>0</sub> | $\mathbf{QS}_1$ | Status                              |

|-----------------|-----------------|-------------------------------------|

| 0               | 0               | No operation                        |

| 0               | 1               | First byte of opcode from the queue |

| 1               | 0               | Empty the queue                     |

| 1               | 1               | Subsequent byte from the queue      |

10.S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>: These are the status signals that provide the status of operation, which is used by the Bus Controller 8288 to generate memory and I/O control signals. These are available at pin 26, 27, and 28. Following is the table showing their status:

| S <sub>2</sub> | $S_1$ | S <sub>0</sub> | Status                    |

|----------------|-------|----------------|---------------------------|

| 0              | 0     | 0              | Interrupt acknowledgement |

| 0              | 0     | 1              | I/O Read                  |

| 0              | 1     | 0              | I/O Write                 |

| 0              | 1     | 1              | Halt                      |

| 1              | 0     | 0              | Opcode fetch              |

| 1 | 0 | 1 | Memory read  |

|---|---|---|--------------|

| 1 | 1 | 0 | Memory write |

| 1 | 1 | 1 | Passive      |

11.LOCK: When this signal is active, it indicates to the other processors not to ask the CPU to leave the system bus. It is activated using the LOCK prefix on any instruction and is available at pin 29.

# **Registers Set**

Registers are fast memory locations within the CPU that are used to create and store the results of CPU operations and other calculations. Different computers have different register sets. They differ in the number of registers, register types, and the length of each register. They also differ in the usage of each register. Registers can be *general-purpose registers* used for multiple purposes and assigned to a variety of functions by the programmer. *Special-purpose registers* are restricted to only specific functions. In some cases, some registers are used only to hold data and cannot be used in the calculations of operand addresses. Data registers' length must be long enough to hold values of most data types. Some machines allow two contiguous registers to hold double-length values. The 8086 registers are classified into *four* types as follow

- 1. Data Registers (General Purpose Registers).

- 2. Pointers and Index Registers.

- 3. Flag Register (Status Register).

- 4. Segment Registers.

#### 1. Data Registers (General Purpose Registers).

There are four registers that are generally used to store both data and addresses. All data registers can be used for arithmetic and logic operations and data movement. each of them has a special use. Each of these registers is 2-bytes (16-bit) long and each is divided into two smaller registers in 1-byte (8-bit) long as follows:

#### 1.1. AX, AH, AL registers

Also known as *the accumulator register*, it is used *to transfer data, access I/O ports, and arithmetic and logical instructions*. The *AX* register is **2 bytes long** and can be divided into two *one-byte registers AH* (A High) and *AL* (*A Low*). The AH register is specially used to store the O/I device number to be handled before using the *INT 21h* interrupt instruction.

#### 1.2. BX, BH, BL registers

Also known as a *Base index register*, BX register usually contains a data pointer used for based. It is used *to hold the address of a procedure or variable*. The **BX** register is **2 bytes long** and can be divided into two **one-byte registers BH** (B High) and **BL** (B Low). The BX register is specially

used to store the starting base address of the memory area within the data segment.

## 1.3. CX, CH, CL registers

Also known as *a Count register*, used in *Loop, shift/rotate instructions and as a counter in string manipulation*. The CX register is 2 bytes long and can be divided into two **one-byte registers CH** (C High) and CL (C Low). The CX register is specially used in loop instruction to store the loop counter.

#### 1.4. DX, DH, DL registers

Also known as *Data register*. It is used as *a port number in I/O operations*. *It is also used in multiplication and division*. The **DX** register is **2 bytes long** and can be divided into two **one-byte registers DH** (D High) and **DL** (D Low). The DX register is specially used to store the address of the string that will be processed before the INT 21 interrupt instruction is used.

#### 2. Pointers and Index Registers

These registers contain the offset of data and instructions. The term *offset refers to the distance of a variable, label, or instruction from its base segment*. The pointers will always store some address or memory location. In 8086 Microprocessor, they usually store the offset through which the actual address is calculated.

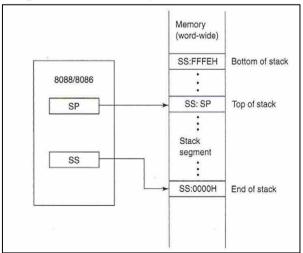

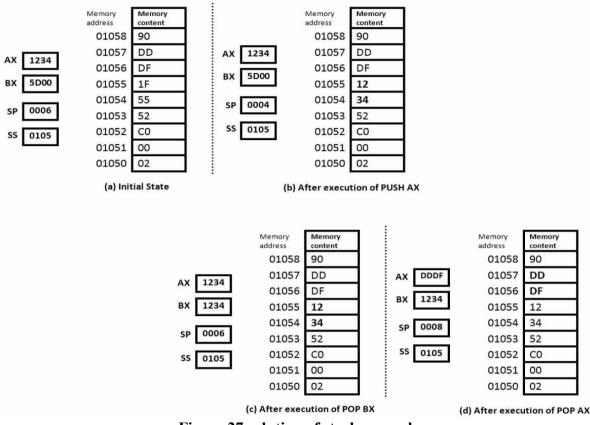

#### 2.1. Stack Pointer (SP)

The Stack Pointer points at the current top value of the Stack. Like the BP, it also acts as an offset to the Stack Segment (SS).

#### 2.2. Base Pointer (BP)

The Base pointer stores the base address of the memory. Also, it acts as an offset for Stack Segment (SS).

#### 2.3. Source Index (SI)

It stores the offset address of the source in string manipulation instructions.

#### 2.4. Destination Index (DI)

It stores the offset address of the Destination in string manipulation instructions.

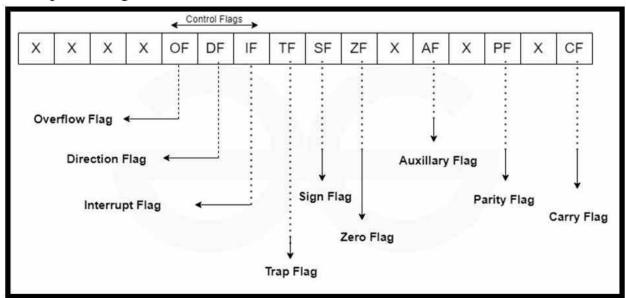

#### 3. Flag Register(Status Register)

It is a 16-bit register, only 9 bits are used as flags and the rest are ignored. These 9 flags provide information about the state of the processor after executing an instruction. The flag bit is changed to 0 or 1 depending on the value of the result after arithmetic or logical operations. The flags used to determine the behavior of many conditional jump and branch instructions. The 9 flags are divided into two groups, 6 for *Conditional Flags* and 3 for *Control Flags*.

#### 3.1. Conditional Flags

It represents the result of the last arithmetic or logical instruction executed. Following is the list of conditional flags:

a) Carry Flag (CF)

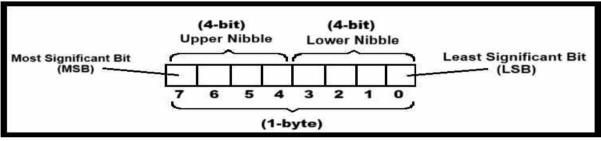

The carry flag (commonly referred to as the C flag) is a single bit in the flag register used to indicate when to Carry/Borrow from the Most Significant Bit (MSB) during mathematical operations. Figure 8 illustrate it.

Figure 8 illustrates the terms most significant bit (MSB), least significant bit (LSB), Upper Nibble, Lower nibble on one byte

#### b) Auxiliary carry Flag (AF)

- This flag is used in BCD (Binary-coded Decimal) operations.

- The status of this flag is updated for every arithmetic or logical operation performed by ALU.

- This flag is set to one if there is a Carry/Borrow for the lower nibble (4 bits) in binary representation, else it is set to zero.

- c) Parity Flag (PF)

This flag is set to 1 when there is an even number of one bits in the result, and to 0 when there is an odd number of one bits. Even if the result is a word only 8 low bits are analyzed.

d) Zero Flag (ZF)

This flag is set to 1 when the result of the arithmetic or the logical operation is zero else it is set to 0.

#### e) Sign Flag (SF)

This flag holds the sign of the result, i.e. when the result of the operation is negative, then the sign flag is set to 1 else set to 0.

#### f) Overflow Flag (OF)

It sets to 1 when there is a signed overflow. For example, when you add signed bytes 100 + 50 (result is not in range -128...127).

#### 3.2. Control Flags

The control flags control the operations of the execution unit. These flags are shown in figure 9. The control flags are as follows:

#### a) Trap Flag (TF)

It is used for single step control and allows the user to execute one instruction at a time for debugging. If it is set, then the program can be run in a single step mode.

#### b) Interrupt Flag (IF)

It is an interrupt enable/disable flag, i.e. it is used to allow/prevent the interruption of a program. It is set to 1 for interrupt enabled condition and set to 0 for interrupt disabled condition.

#### c) Direction Flag (DF)

This flag is used by some instructions to process data string, when this flag is set to 0 - the processing is done forward, when this flag is set to 1 the processing is done backward.

**Figure 9 Flag Register**

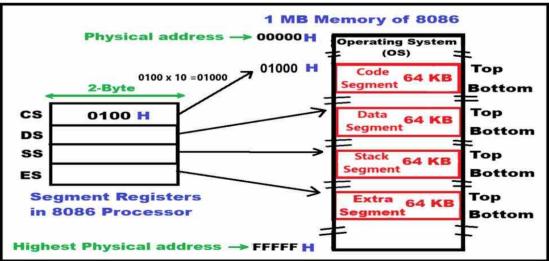

#### 4. Segment Registers

The processor can divide the main memory into four Segments (Sections) which are: *Code Segment, Data Segment, Stack Segment, and Extra Segment.* For this reason, the BIU has four segments' registers, each 2 bytes long, and are used to store the addresses of the beginnings of the four Segment. The processor uses the addresses stored in these registers to determine the physical address and access any memory location in those segments figure 10 shows the segment registers. These registers are:

#### 4.1. Code segment register (CS)

The CS register holds the base address of the code segment area in the memory. In this area of memory, the executable program instructions are stored.

#### 4.2. Data Segment register (DS).

The DS register holds the base address of the data segment area in memory. In this area of memory, the stored data, variables and arrays are declared in the program.

#### 4.3. Extra Segment register (ES)

The ES register holds the base address of the extra segment area in memory. In this area of memory more data, variables and arrays declared in the program are stored.

#### 4.4.Stack Segment register (SS)

The SS register holds the base address of the Stack segment area in memory. This area of memory is used as a stack where data is stored according to the "first in, last out" (FILO) principle.

Figure 10 Segment Registers and 1MB Memory

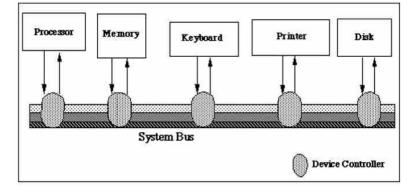

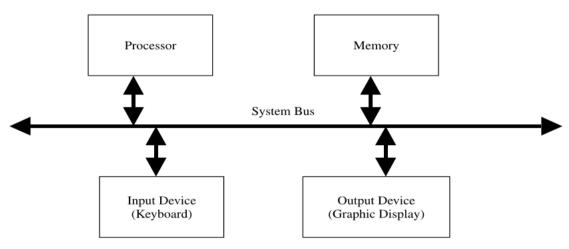

# **System Buses**

#### **Bus structure**

The system bus connects the CPU (Processor), memory and peripherals devices (input/output device or secondary memory) with each other. The bus system carries data, address and control information. The speed of the system bus is the part of performance of computer system figure 11 shows the system buses.

Note: The components of the computer system communicate with each other and with the outside world through system bus. The processor connects to memory and peripheral devices by bus system.

*A* **Bus** is a bunch of wires, and electrical path on the printed IC to which everything in the system is connected.

There are three types of Buses

- 1. Address Buss (AB): is unidirectional (one direction) because address flow in one direction from processor to memory or from processor to input/ output devices. The width of AB determines the amount of physical memory addressable by the processor.

- 2. **Data Bus (DB):** Is bidirectional (two directions) because allow data to transfer between the processor (CPU) and memory (RAM). the width of DB indicates the size of the data transferred between the processor and memory or I/O device.

- 3. **Control Bus (CB):** is bidirectional (two directions) used by CPU for communicating with other devices within the computer. It carries control signals from CPU. The typical control signals include memory read, memory write, I/O read, I/O write, bus request. These signals indicate the type of action taking place in the computer system.

Figure 11 The system bus

# Memory (Main Memory or Primary memory (RAM))

The primary memory (RAM) is a temporary storage area. It holds the data and instruction that the CPU needs. The memory of a computer system consists of tiny electronics witches, with each switch set in one of two states: open or close. It is however more convenient to think of these states as 0 and 1. Thus each switch can represent a binary digit or bit, as it is known, the memory unit consists of millions of such bits, bits are organized into groups of eight bits called byte. Memory can be viewed as consisting of an ordered sequence of bytes. Each byte in this memory can be identified by its sequence number starting with 0, as shown in Figure 12. This is referred to as memory address of the byte. Such memory is called byte addressable memory. The memory address space of a system is determined by the address bus width of the CPU used in the system.

Figure 12 Logical view of the system memory

# Two basic memory operations:

The memory unit supports two fundamental operations: Read and Write. The read operation read a previously stored data and the write operation stores a value in memory.

## Steps in a typical <u>Read cycle</u>:

- **1.** Place the address of the location to be read on the address bus.

- 2. Activate the memory read control signal on the control bus.

- **3.** Wait for the memory to retrieve the data from the address memory location.

- **4.** Read the data from the data bus.

- **5.** Drop the memory read control signal to terminate the read cycle.

# Steps in a typical <u>Write cycle</u>:

- 1. Place the address of the location to be written on the address bus.

- 2. Place the data to be written on the data bus.

- 3. Activate the memory write control signal on the control bus.

- 4. Wait for the memory to store the data at the address location.

- 5. Drop the memory write control signal to terminate the write cycle.

# Addresses

Group of bits which are arranged sequentially in memory, to enable direct access, a number called address is associated with each group. Addresses start at 0 and increase for successive groups. The term location refers to a group of bits with a unique address. Table 5 represents Bit, Byte, and larger units.

| Table 5 address units |                                                   |  |  |  |  |

|-----------------------|---------------------------------------------------|--|--|--|--|

| Name                  | Number of Byte                                    |  |  |  |  |

| Bit                   | 0 or 1                                            |  |  |  |  |

| Byte                  | is a group of bits used to represent a character, |  |  |  |  |

|                       | typically 8-bit.                                  |  |  |  |  |

| Word                  | 2-byte (16-bit)                                   |  |  |  |  |

| Double                | 4-byte (32-bits)                                  |  |  |  |  |

| Word                  |                                                   |  |  |  |  |

| Quad word             | 8-byte (64-byte)                                  |  |  |  |  |

| Name      | Number of Byte                                    |  |  |

|-----------|---------------------------------------------------|--|--|

| Kilo Byte | The number 210=1024=1 KB thus                     |  |  |

| (KB)      | 640K=640*1024=655360 bytes)                       |  |  |

| Megabyte  | (1024*1024) byte or 1,048,576 byte) approximately |  |  |

| (MB)      | 1,000,000 bytes                                   |  |  |

| Gigabyte  | (1024*1024*10240byte) or (1,073,741,824 byte),    |  |  |

| (GB)      | approximately 1,000,000,000 bytes.                |  |  |

| Terabyte  | Approximately 1,000,000,000,000 bytes.            |  |  |

| (TB)      |                                                   |  |  |

# **Memory Chips**

Memory chips have two main properties that determine their application, storage capacity or size and access time or speed. A memory chip contains a number of locations, each of which stores one or more bits of data known as its bit width. The storage capacity of a memory chip is the product of the number of locations and the bit width. For example, a chip with 512 locations and a 2-bit data width has a memory size of  $512 \times 2=1024$  bits.

Since the standard unit of data is a byte (8 bits), the above storage capacity is normally given as 1024/8 = 128 bytes.

The number of locations may be obtained from the address width of the chip. For example, a chip with 10 address lines has  $2^{10}$ = 1024 or 1 k locations. Given an 8-bit data width, a 10- bit address chip has a memory size of  $2^{10} \times 8$ = 1024×8 = 1k ×1 byte = 1 KB. The computer's word size can be expressed in bytes as well as in bits.

For example, a word size of 8-bit is also a word size of one byte; a word size of 16- bit is a word size of two byte. Computers are often described in terms of their word size, such as an 8-bit computer, a 16-bit computer and so on.

For example, a 16-bit computer is one in which the instruction data are stored in memory as 16-bit units, and processed by the CPU in 16-bit units. The word size also indicates the size of the <u>data bus</u> which carries data between the CPU and memory and between the CPU and I/O devices. To access the memory, to store or retrieve a single word of information, it is necessary to have a unique address.

The word address is the number that identifies the location of a word in a memory. Each word stored in a memory device has a unique address.

Addresses are always expressed as binary number, although hexadecimal and decimal numbers are often used for convenience.

The second property of memory chips is the access time, access time is the speed with which a location within the memory chip may be made a variable to the data bus. It is defined as the time interval between the instant that an address is sent to the memory chip and the instant that the data stored in to the location appears on the data bus. Access time is given in nanosecond (ns) and varies from 25 ns to the relatively slow 200 ns.

# **NOTES:**

- The large computers (mainframes) have word-sizes that are usually in the 32-to-64 –bits range.

- Mini computers have a word size from 8-to-32-bits range.

- Microcomputers have a word size from 4-to-32-bits range.

In general, a computer with a larger word size, can execute programs of instruction at a fast rate because more data and more instruction are stuffed into one word. The larger word sizes, however, mean more lines making up the data bus, and therefore more interconnections between the CPU and memory and I/O devices.

The word size is 4-bit therefore there are 4-data I/P lines and 4-data O/P lines. This memory has 32 different words, and therefore has 32 different addresses (storage location) from (00000) to (11111). Thus, we need a 5 address I/P lines.

# Memory capacity = number of memory storage Location ×size of each word

# = (number of word ) × (number of bits per word) = m (word)\*n(bits) = m\*n bits

**The capacity of memory** depends on two parameters, the number of words (m) and the number of bits per word (n).

Every bit added to the length of address will double the number of words in the memory. The increase in the number of bits per bits requires that an increase the length of data I/P and data O/P lines.

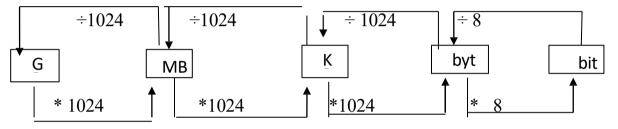

# Memory capacity units

| Byte | $\rightarrow$ | 8bits     |  |  |

|------|---------------|-----------|--|--|

| VD   | _             | 1021 Duto |  |  |

| ND | 1024 Dyte   |

|----|-------------|

| MB | <br>1024 KB |

- $\begin{array}{rcl} MB & \longrightarrow & 1024 \text{ KB} \\ GB & \longrightarrow & 1024 \text{ MG} \end{array}$

- TB  $\rightarrow$  1024 GB

Figure 13 shows the unit of memory capacity measurement.

Figure 13 memory capacity measurements

#### Examples

- If the capacity of memory is 2MG, what is the capacity in KB ?

Solution: the capacity in KB

Capacity = 2\*1024= 2048 KB

- 2. the capacity of memory is 10MG, what is the capacity in byte?

Solution: The capacity in byte

Capacity = 10\*1024 \*1024 = 10485760

- 3. the capacity of memory is 2MG, what is the capacity in bit  $2^{1024*1024*8} = 16777216$  bits

- 4. if the capacity of memory is 16 bits, what is the capacity in Byte?Solution: the capacity in byte

**Capacity** = 16/8 = 2 byte

- 5. the capacity of memory is 20 KB, what is the capacity in MG? Solution: the capacity in MG capacity = 20/ 1024=0.01953125 MG

- 6. the capacity of memory is 15 KB, what is the capacity in GB? Solution: the capacity in KB

Capacity = 15/1024 / 1024 = 0.0000143051 GB

#### **Memory example**

**Example1** A certain memory chip is specified as 2K×8:

- 1. How many words can be stored on this chip?

- 2. What is the words size?

- 3. How many total bits can this chip store?

#### **SOLUTION:**

- 1.  $2K = 2 \times 1024 = 2048$  words(bytes)

- 2. The word size is 8-bits (1 byte).

- 3. Capacity =  $2048 \times 8 = 16384$  bits. Memory chip

**Example2:** A certain memory chip is specified as  $2K \times 16$

- 1. How many words can be stored on this chip?

- 2. What is the words size?

- 3. How many total bits can this chip store?

#### Solution:

- 1.  $2K = 2 \times 1024 = 2048$  words

- 2. The word size is 16-bits(2 byte).

- 3. Capacity = 2048 \* 16 = 32768 bits.

**Example3:-** Which memory stores the most number of bits:  $2MG \times 8$  memory or  $2MG \times 16$  memory?

#### Solution:

$2MG = 2 \times 1024 \times 1024 = 2 \times (1048576)$  =words

- 1. Capacity 2MG  $\times 8 = (2 \times 1024 \times 1024) \times 8 = 16,777,216$  bits.

- 2. Capacity 2MG  $\times 16 = (2 \times 1024 \times 1024) \times 16 = 33,554,432$  bits.

So  $2MG \times 16$  memory is bigger than  $2MG \times 8$

**Example4:** Which memory stores the greatest number of bits:  $4MG \times 8$  memory or  $2MG \times 16$ ?

#### **Solution:**

- 1. Capacity =  $(4 \times 1024 \times 1024) \times 8 = 33,554,432$  bits.

- 2. Capacity =  $(2 \times 1024 \times 1024) \times 16 = 33,554,432$  bits.

#### **Example5:** A certain memory has a capacity of $4K \times 8$

- 1. How many data I/P & data O/P lines?

- 2. How many word address line?

- 3. What is its capacity in byte?

#### Solution

- 1. 8 each line: So, data I/P lines = data O/P lines =8

- 2.  $4 \times 1024 = 4096$  words(bytes) Thus, there are 4096 memory addresses  $2^{12} = 4096$

- So, it required a 12- bit address line

- 3. The capacity = (4 ×1024) × 8= 32,768 bit = 32,769/8 =4096 byte (since 1byte = 8 bit).

#### **Example6:** - the a certain memory has a capacity of $4K \times 16$

- 1. How many data I/P & data O/P lines?

- 2. How many word address lines?

- 3. What is its capacity in byte?

#### **Solution:**

- 1. 16 each one. Data I/P lines = data O/P lines =16

- 2.  $4 \times 1024 = 4096$  words

Thus, there are 4096 memory addresses.

$4096 = 2^{12}$  so, its require a 12-bit address line.

3. Capacity =  $(4 \times 1024) \times 16 = 65,536$  bit = 65,536 / 8 = 8.192 byte

H.W: A computer system has **8bits data I/P** & data **O/P lines** and 12-**bit address bus (address lines)** find the **capacity of memory** in **bits and KB**.

# **Memory Types and Physical addressing**

#### **Memory Representation**

The computer memory stores different kinds of data like input data, output data, intermediate results, etc., and the instructions. *Binary digit* or *bit* is the basic unit of memory. A *bit* is a single binary digit, i.e., 0 or 1. A bit is the smallest unit of representation of data in a computer. However, the data is handled by the computer as a combination of bits. A group of 8 bits form a **byte**. One byte is the smallest unit of data that is handled by the computer. One byte (8 bit) can store  $2^8 = 256$  different combinations of bits, and thus can be used to represent 256 different symbols. In a byte, the different combinations of bits fall in the range 00000000 to 11111111. A group of bytes can be further

combined to form a word. A word can be a group of 2, 4 or 8 bytes.

1 bit = 0 or 1 1 Byte (B) = 8 bits 1 Kilobyte (KB) =  $2^{10}$  = 1024 bytes 1 Megabyte (MB) =  $2^{20}$  = 1024KB 1 Gigabyte (GB) =  $2^{30}$  = 1024 MB = 1024 \*1024 KB 1 Terabyte (TB) =  $2^{40}$ = 1024 GB = 1024 \* 1024 \*1024 KB

#### I. Characteristics Of Memories

#### - Volatility

- Volatile {RAM}

- Non-volatile {ROM, Flash memory}

- Mutability

- Read/Write {RAM, HDD, SSD, RAM, Cache, Registers...}

Read Only {Optical ROM (CD/DVD...), Semiconductor

- ROM}

- Accessibility

- Random Access {RAM, Cache}

- Direct Access {HDD, Optical Disks}

- Sequential Access {Magnetic Tapes}

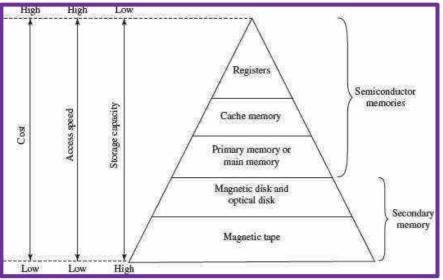

# **II. Memory Hierarchy**

The memory is characterized on the basis of two key factors: *capacity* and *access time*.

- *Capacity* is the amount of information (<u>in bits</u>) that a memory can store.

- *Access time* is the time interval between the read/ write request and the availability of data. The lesser the access time, the faster is the *speed of memory*.

Ideally, we want the memory with *fastest speed and largest capacity*. However, the cost of fast memory is very high. The computer uses a hierarchy of memory that is organized in a manner to enable the fastest speed and largest capacity of memory.

The hierarchy of the different memory types is shown in Figure 14.

Figure 14 Memory hierarchy

**The Internal Memory** and **External Memory** are the two broad categories of memory used in the computer. *The Internal Memory* consists of the CPU registers, cache memory and primary memory. The internal memory is used by the CPU to perform the computing tasks. *The External Memory* is also called the **secondary memory**. The secondary memory is used to store the large amount of data and the software.

In general, referring to <u>the computer memory</u> usually means <u>the internal</u> <u>memory</u>.

#### • Internal Memory

The key features of internal memory are:

- 1. Limited storage capacity.

- 2. Temporary storage.

- 3. Fast access.

- 4. High cost.

*Registers, cache memory*, and *primary memory* constitute the internal memory. *The primary memory* is further of two kinds: RAM and ROM. *Registers* are the fastest and the most expensive among all the memory types. The registers are located inside the CPU, and are directly accessible by the CPU. The speed of registers is between 1-2 ns (nanosecond). The sum of the size of registers is about 200B. *Cache memory* is next in the hierarchy and is placed between the CPU and the main memory. The speed of cache is between 2-10 ns. The cache size varies between 32 KB to 4MB. Any program or data that has to be executed must be brought into RAM from the secondary memory. Primary memory is relatively slower than the cache memory. The speed of RAM is around 60ns. The RAM size varies from 512KB to 64GB.

#### • Secondary Memory

The key features of secondary memory storage devices are:

- 1. Very high storage capacity.

- 2. Permanent storage (non-volatile), unless erased by user.

- 3. Relatively slower access.

- 4. Stores data and instructions that are not currently being used by CPU but may be required later for processing.

- 5. Cheapest among all memory.

To get the fastest speed of memory with largest capacity and least cost, the fast memory is located close to the processor. The secondary memory, which is not as fast, is used to store information permanently, and is placed farthest from the processor.

With respect to CPU, the memory is organized as follows:

- *Registers* are placed inside the CPU (small capacity, high cost, very high speed)

- Cache memory is placed next in the hierarchy (inside and outside the

CPU)

- *Primary memory* is placed next in the hierarchy

- Secondary memory is the farthest from CPU (large capacity, low cost, low speed) The speed of memories is dependent on the kind of technology used for the memory. The registers, cache memory and primary memory are semiconductor memories. They do not have any moving parts and are fast memories. The secondary memory is magnetic or optical memory has moving parts and has slow speed.

#### **III. CPU Registers**

**Registers** are very high-speed storage areas located inside the CPU. After CPU gets the data and instructions from the cache or RAM, the data and instructions are moved to the registers for processing. Registers are manipulated directly by the control unit of CPU during instruction execution. That is why registers are often referred to as the CPU's *working memory*. Since CPU uses registers for the processing of data, the number of registers in a CPU and the size of each register affect the power and speed of a CPU. The more the number of registers (ten to hundreds) and bigger the size of each register (8 bits to 64 bits), the better it is.

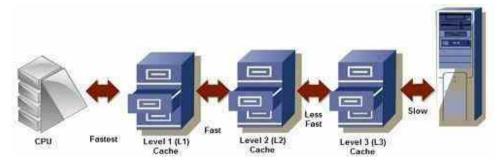

#### IV. Cache Memory

Cache memory is placed in between the CPU and the RAM. Cache memory is a fast memory, faster than the RAM. When the CPU needs an instruction or data during processing, it first looks in the cache. *If the information is present in the cache*, it is called a *cache hit*, and the data or instruction is retrieved from the cache. *If the information is not present in cache*, then it is called a *cache miss* and the information is then retrieved from RAM.

# **Type of Cache memory**

Cache memory improves the speed of the CPU, but it is expensive. Type of Cache Memory is divided into different levels that are L1, L2, L3:

#### Level 1 (L1) cache or Primary Cache

L1 is the primary type cache memory. The Size of the L1 cache very small comparison to others that is between *2KB to 64KB*, it depends on computer processor. It is an embedded register in the computer microprocessor (CPU). The Instructions that are required by the CPU that are firstly searched in L1 Cache. Example of registers are accumulator, address register, Program

#### Microprocessor

#### counter etc.

#### Level 2 (L2) cache or Secondary Cache

L2 is secondary type cache memory. The Size of the L2 cache is more capacious than L1 that is between **256KB to 512KB**. L2 cache is located on computer microprocessor. After searching the Instructions in L1 Cache, if not found then it searched into L2 cache by computer microprocessor. The high-speed system bus interconnecting the cache to the microprocessor.

#### Level 3 (L3) cache or Main Memory

The L3 cache is larger in size but also slower in speed than L1 and L2, its size is between *IMB to 8MB*. In Multicore processors, each core may have separate L1 and L2, but all cores share a common L3 cache. L3 cache double speed than the RAM.

The advantages and disadvantages of cache memory are as follows:

#### Advantages

The advantages of cache memory are as follows:

- Cache memory is faster than main memory.

- It consumes less access time as compared to main memory.

- It stores the program that can be executed within a short period of time.

- It stores data for temporary use.

#### Disadvantages

The disadvantages of cache memory are as follows:

- Cache memory has limited capacity.

- It is very expensive.

#### V. PRIMARY MEMORY (Main Memory)

Primary memory is the main memory of computer. It is a chip mounted on the motherboard of computer. Primary memory is categorized into two main types: Random access memory (ram) and read only memory (rom). **RAM** is used for the temporary storage of input data, output data and intermediate results. The

#### Microprocessor

input data entered into the computer using the input device, is stored in RAM for processing. After processing, the output data is stored in RAM before being sent to the output device. Any intermediate results generated during the processing of program are also stored in RAM. Unlike RAM, the data once stored in **ROM** either cannot be changed or can only be changed using some special operations. Therefore, ROM is used to store the data that does not require a change.

#### **Types of Primary Memory**

#### 1. RAM (Random Access Memory)

The Word "**RAM**" stands for "random access memory" or may also refer to short- term memory. It's called "random" because you can read store data randomly at any time and from any physical location. It is a temporal storage memory. RAM is volatile that only retains all the data as long as the computer powered. It is the fastest type of memory. RAM stores the currently processed data from the CPU and sends them to the graphics unit.

#### There are generally two broad subcategories of RAM:

- Static RAM (SRAM): Static RAM is the form of RAM and made with flipflops and used for primary storage are volatile. It retains data in latch as long as the computer powered. SRAM is more expensive and consumes more power than DRAM. It used as Cache Memory in a computer system. As technically, SRAM uses more transistors as compared to DRAM. It is faster compared to DRAM due to the latching arrangement, and they use 6 transistors per data bit as compared to DRAM, which uses one transistor per bit.

- **Dynamic Random Access Memory (DRAM)**: It is another form of RAM used as Main Memory, its retains information in Capacitors for a short period (a few milliseconds) even though the computer powered. The Data is Refreshed Periodically to maintain in it. The DRAM is cheaper, but it can store much more information. Moreover, it is also slower and consumes less power than SRAM.

#### 2. ROM (Read Only Memory)

ROM is the long-term internal memory. ROM is "Non-Volatile Memory" that retains data without the flow of electricity. ROM is an essential chip with

permanently written data or programs. It is similar to the RAM that is accessed by the CPU. ROM comes with pre-written by the computer manufacturer to hold the instructions for booting-up the computer.

There is generally three broad type of ROM:

- **PROM (Programmable Read Only Memory)**: PROM stands for programmable ROM. It can be programmed only be done once and read many. Unlike RAM, PROMs retain their contents without the flow of electricity. PROM is also nonvolatile memory. The significant difference between a ROM and a PROM is that a ROM comes with pre-written by the computer manufacturer whereas PROM manufactured as blank memory. PROM can be programmed by PROM burner and by blowing internal fuses permanently.

- **EPROM (Erasable Programmable Read Only Memory)**: EPROM is pronounced ee-prom. This memory type retains its contents until it exposed to intense ultraviolet light that clears its contents, making it possible to reprogram the memory.

- EEPROM (Electrically Erasable Programmable Read Only Memory): EEPROM can be burned (programmed) and erased by first electrical waves in a millisecond. A single byte of a data or the entire contents of device can be erased. To write or erase this memory type, you need a device called a PROM burner.

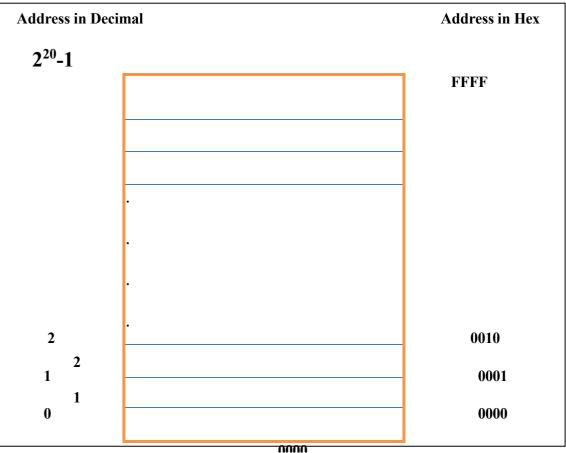

# **Physical Addressing**

Addresses are group of bits which are arranged sequentially in memory, to enable direct access, a number called address is associated with each group. Addresses start at 0 and increase for successive groups. The term location refers to a group of bits with a unique address.

#### Addresses type

There are three types of addresses.

- 1- Physical address.

- 2- Offset address.

- 3- Logical address.

#### Microprocessor

#### 1. Physical Address (PA)

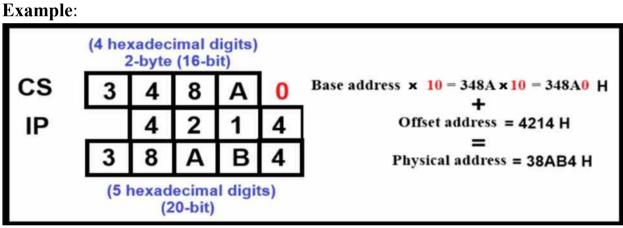

The physical address is the 20- bit address that actually put on the address pins of the 8086 microprocessors. The 8086 microprocessor handles 1 MB of memory and has an address range from 00000 H to FFFFF H. Since each hexadecimal digit is represented by 4-bits, so each memory address requires 20-bits to represent the 5 digits of physical address.

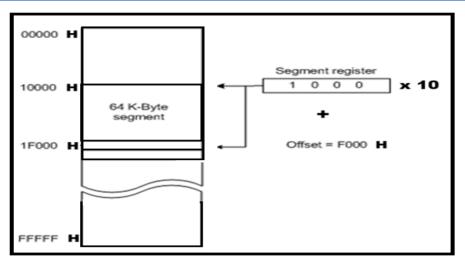

### **Physical address Generation**

A 2-byte register can only store 4 hexadecimal digits (16 bits). So, the address stored in the segment register (Base address) is multiplied by 10 H (or shifting it 4 digits to the left or adding zeros to the bottom 4 bits) to get 5 hexadecimal digits of the physical address (20 bits) and then the offset address is added as in the following equation. Figure 15 shows how the physical address is generated.

Physical address = Base address x 10 + Offset address.

Figure 15 Physical address Generation

#### **Offset address**

Offset is the displacement of the memory location from the starting location of the memory segment (Data, Extra, Stack, or Code). The complete physical address which is 20-bits long is generated using segment and offset registers each of the size 16-bit. So, the addresses stored in these registers range from 0000 H to FFFF H. In Other word, offset address is the number of address locations added to a base address in order to get to a specific absolute address. See figure 16.

Figure 16 the implementation of offset address

#### Segment and Offset Registers

Segment registers contain base addresses for segments and each of these registers handles a specific type of register that contains offset addresses. By combining the base address and the offset address, the physical address is generated as shown in the following table:

| Table o physical address |                 |                                                   |  |  |  |

|--------------------------|-----------------|---------------------------------------------------|--|--|--|

| Segment register         | Offset register | Physical address                                  |  |  |  |

| CS IP                    |                 | Instruction address                               |  |  |  |

| SS                       | SP, BP          | Stack address                                     |  |  |  |

| DS BX, DI, SI            |                 | Data address                                      |  |  |  |

| ES                       | BX, DI, SI      | String destination address for string instruction |  |  |  |

Table 6 physical address

# Logical address (virtual address)

A logical address is an address generated by the CPU during program execution that refers to a location in the memory space. It acts as a reference point for where data or instructions are stored within a program. The logical address consists of the segment base address (located in the segment register) and the offset address and it is represented by the following format (**Segment :Offset**).

# Q:/ What is the difference between logical and physical address in 8086? Answer

Logical address is generated by CPU in perspective of a program whereas the physical address is a location that exists in the memory unit.

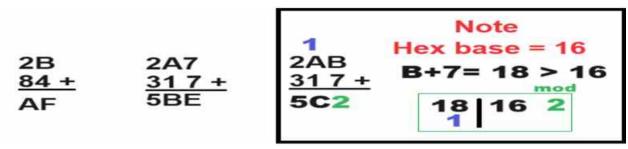

Examples shows how to add numbers in hexadecimal system which is used to calculate memory locations

Figure 17 adding numbers

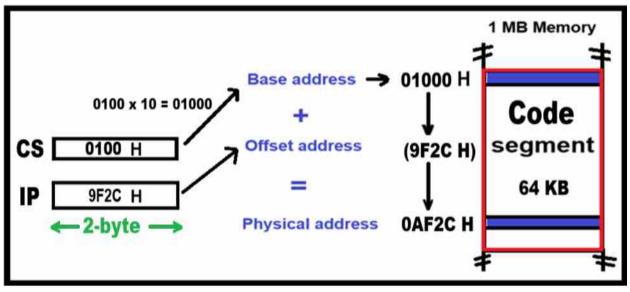

#### Q8: How physical address is calculated in 8086 explain with example?

The 8086 addresses a segmented memory. The complete physical address which is 20-bits long is generated **using segment and offset registers each of the size 16-bit**. The content of a segment registers also called as segment address, and content of an offset register also called as offset address.

#### **Example:**

If CD = 0100 H and IP = 9F2C H, determine the **physical address**.

#### Solution (steps are shown in figure 18):

Physical address = Base address  $\times$  10 + Offset address

$= 0100 \times 10 + 9F2C$ = 01000 + 9F2C = 0AF2C H

Figure 18 Determining the physical address

#### Example 1:

If DS = 24F6 H and SI = 634A H, **determine**:

a- The offset address

b- The physical address

### class: 2<sup>nd</sup> stage

#### Microprocessor

c- The logical address d- The lower range of the Data segment e- The upper range of the Data segment **Solution**: a- 634A H b- 24F6 x 10 + 634A = 2B2AA H c- 24F6: 634A d- 24F6 x 10 + 0000 = 24F60 H e- 24F6 x 10 + FFFF = 34F5F H

#### Example 2:

If SS=7FA2 H and SP= 438E H, determine: a- The offset address b- The physical address c- The logical address d- The lower range of the Stack segment e- The upper range of the Stack segment **Solution:** a- 438E H b- 7FA20 + 438E = 83DAE H c- 7FA20 + 438E d- 7FA20 + 0000 = 7FA20 H

e-7FA20 + FFFF = 8FA1F H

# **Input/ Output devices**

Input / Output (I/O) devices provide the means by which the computer system can interact with the outside world. Computers use I/O devices (also called peripheral devices) for two major purposes:

- 1. To communicate with the outside world and,

- 2. Store data.

Input devices (even output devices) can be distinguished from each other by their *data processing rate* which means the average number of characters that can be processed by a device per second.

For example, the data processing rate for *the keyboard* is about 10 characters (bytes)/second, a *scanner* can send data at a rate of about 200,000 characters/second. Similarly, while *a laser printer* can output data at a rate of about 100,000 characters/second, a *graphic display* can output data at a rate of about 30,000,000 characters/second.

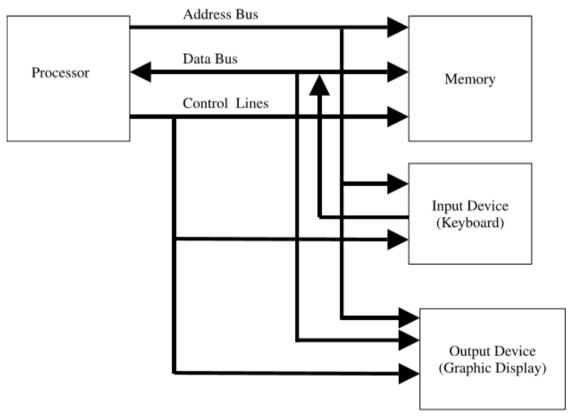

A simple arrangement for connecting the processor and the memory in a given computer system to an input device, for example, a keyboard and an output device such as a graphic display. A single bus consisting of the required address, data, and control lines is used to connect the system's components is shown in **Figure 19**.

Figure 19 A single bus system

*I/O protocol* is a simple way of communication between the processor and I/O devices, it requires the availability of the input and output registers. In a typical computer system, there is a number of input registers, each belonging to a specific

input device. There is also a number of output registers, each belonging to a specific output device.

More than one arrangement exists to satisfy these requirements. Among these, two particular methods are *Isolated I/O and Memory-Mapped I/O*.

# Isolated I/O

Isolated I/O also called *Shared I/O*, is a method for managing I/O devices in a computer system. *In the isolated I/O configuration*, a distinct address space is assigned for I/O devices separated from the memory address space. the CPU uses specific instructions (like IN and OUT) to communicate with I/O devices, these instructions are different from the ones used to access memory. Isolated I/O often utilizes separate control lines for I/O operations, distinguishing them from memory operations.

The main advantage of Isolated I/O is *the separation between the memory address space and that of the I/O devices*. While the main disadvantage is *the need to have special input and output instructions in the processor instruction set.* Figure 20 shows the arrangement of Isolated I/O devices.

Figure 20 Isolated I/O arrangement

#### Memory mapped I/O

Memory-mapped I/O is a technique where input/output (I/O) devices and main memory share the same address space. This means that the CPU can interact with I/O devices using the same instructions it uses to access memory (like LOAD, Store. In this configuration there is no *dedicated control lines* for I/O operations. Instead, the same control lines used for memory access are also used for I/O. figure 21 show the memory mapped arrangement.

The **main advantage** of the memory-mapped I/O is the use of the read and write instructions of the processor to perform the input and output operations, respectively. It eliminates the need for introducing special I/O instructions. The **main disadvantage** of the memory-mapped I/O is the need to reserve a certain part of the memory address space for addressing I/O devices, that is, a reduction in the available memory address space.

Figure 21 the memory mapped arrangement

# **Modes of Transfer**

Data transfer between the processor and I/O devices may be handled in a variety of modes. three possible modes are Programmed I/O, Interrupt I/O and Direct Memory Access (MDA).

# **Programmed I/O**

In this mode of the data transfer, the I/O operations are performed under the control of the CPU. A complete instruction fetches, decode, and execute cycle will have to be executed for every input and every output operation. The CPU sends commands to the I/O device, waits for the device to become ready, and then transfers the data. It is a simple method but its main disadvantage is that, the CPU is heavily involved and spends a lot of time waiting for the I/O device (wasting the CPU time), which is inefficient.

# **Interrupt-Driven I/O**

Before we explain this mode of data transfer between the processor and I/O device, we will know what is an interrupt and how the CPU responds to it.

An *interrupt* is a signal to the processor that an event has occurred that requires its attention. This event can be triggered by various sources, such as: I/O devices (data transfer), hardware errors (disk failure) or software events (a program making a system call).

When the CPU is interrupted, it is required to discontinue its current activity, attend to the interrupting condition (serve the interrupt), and then resume its activity from wherever it stopped. Discontinuity of the processor's current activity requires finishing executing the current instruction, saving the processor status (mostly in the form of pushing register values onto a stack), and transferring control (jump) to what is called the *interrupt service routine* (ISR). The service offered to an interrupt will depend on the source of the interrupt. For example, *in the case of an I/O interrupt, serving an interrupt means to perform the required data transfer*. Upon finishing serving an interrupt, the processor should restore the original status by popping the relevant values from the stack. Once the processor returns to the normal state, it can enable sources of interrupt again.

In the *interrupt-Driven I/O* the CPU initiates the I/O operation and then goes on to perform other tasks. When the I/O device is ready to transfer data, it sends an interrupt signal to the CPU. The CPU then handles the interrupt and transfers the data. The advantage of this transfer mode, it is more efficient than programmed I/O as the CPU is not constantly waiting. Its disadvantage is that it still requires the CPU intervention for each data transfer, which can be overhead for large data transfers.

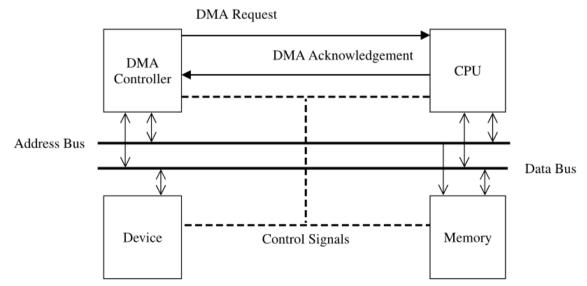

# **Direct Memory Access (DMA)**

The main idea of direct memory access (DMA) is to enable peripheral devices to transfer data directly from and to memory without the intervention of the CPU. This mechanism allows the CPU to do other work, which would lead to improved performance, especially in the cases of large transfers.

The DMA controller is a piece of hardware that controls one or more I/O devices. It allows direct data transfer between I/O devices and the system's memory without the help of the processor. In a typical DMA transfer, some event notifies the DMA controller that data needs to be transferred to or from memory. Both the DMA and CPU use memory bus and only one or the other can use the memory at the same time. The DMA controller requests CPU permission to use a bus, which is granted by the CPU. The DMA then conducts memory transfer independently, and after completion it leaves the control to the CPU. Figure 22 shows how the DMA controller shares the CPU's memory bus.

Figure 22 DMA controller shares the CPU's memory bus

# **Instruction Set and Format**

#### **Microprocessor - 8086 Instruction Sets**

Instructions can be classified based on the number of operands as: three-address, two-address, one-and-half-address, one-address, and zero-address.

A three-address instruction takes the form operation add-1, add-2, add-3. In this form, each of add-1, add-2, and add-3 refers to a register or to a memory location. For example, the instruction  $ADD R_1$ ,  $R_2$ ,  $R_3$ . This instruction indicates that the operation to be performed is addition. It also indicates that the values to be added are those stored in registers  $R_1$  and  $R_2$  and the results should be stored in register  $R_3$ .

A two-address instruction takes the form operation add-1, add-2. In this form, each of add-1 and add-2 refers to a register or to a memory location. For example, the instruction  $ADD R_1, R_2$ . This instruction adds the contents of register  $R_1$  to the contents of register  $R_2$  and stores the results in register  $R_2$ . The original contents of register  $R_2$  are lost due to this operation while the original contents of register  $R_1$  remain intact.

*A one-address instruction* takes the form ADD  $R_1$ . In this case the instruction implicitly refers to a register, called the Accumulator  $R_{acc}$ , such that the contents of the accumulator is added to the contents of the register  $R_1$  and the results are stored back into the accumulator  $R_{acc}$ .

The 8086 microprocessor supports 8 types of instructions

- 1. Data Transfer Instructions

- 2. Arithmetic Instructions

- 3. Bit Manipulation Instructions

- 4. String Instructions

- 5. Branch Instructions

- 6. Processor Control Instructions

- 7. Loop & Iteration Instructions

- 8. Interrupt Instructions

Let us now discuss these instruction sets in detail.

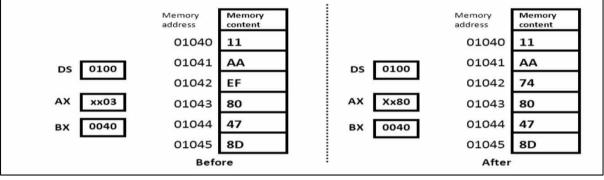

#### 1. Data Transfer Instructions

These instructions are used to transfer the data from the source operand to the destination operand. The data can be of any type. They are classified into four groups as explain in table 7.

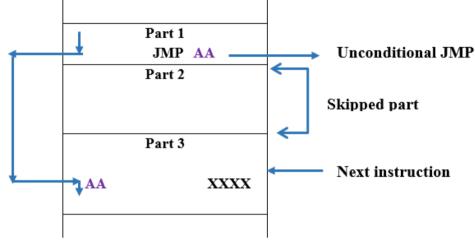

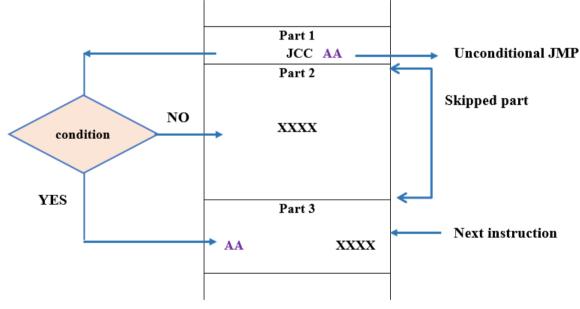

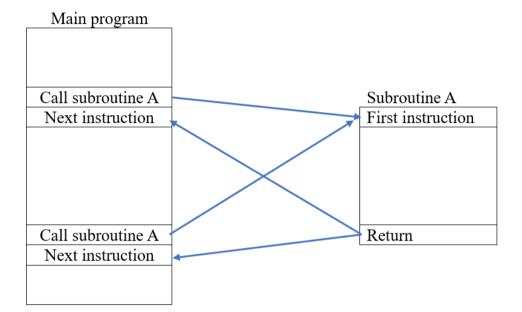

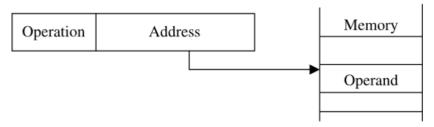

| General-purpose Byte | Special address | Simple input/output | Flag transfer |  |  |  |