University of Technology- Computer Science

# **Computer Architecture**

Third Class 2023-2024

Asst. Prof Dr. Raheem Abdul Sahib

# Computer Architecture Lecturers: Asst. Prof. Dr. Raheem Abdul Sahib Ogla

2023-2024 Second Course Part One

Computer Architecture – 2nd course (syllabus)

Introduction to Computer Organization

- RISC and CISC

- I/O Organization and Peripheral Control Strategies.

- I/O Interfaces and Programming

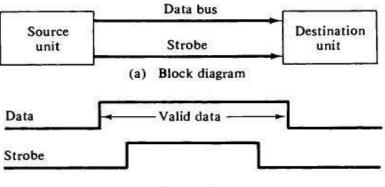

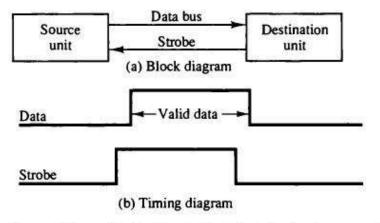

- Asynchronous data transfer

# ➤ Memory Management.

- Memory types and Hierarchy

- Main Memory address map.

- Associative Memory and Content Addressable Memories.

# ► Parallel Processing

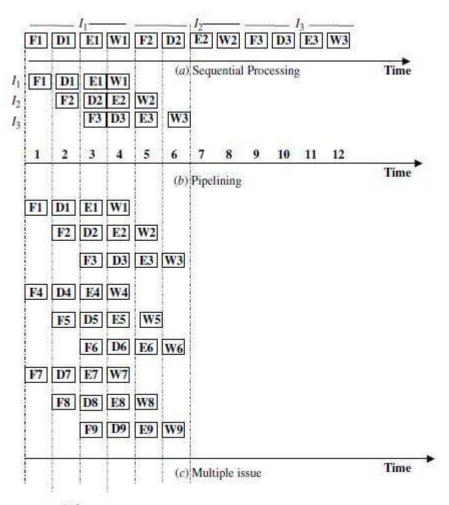

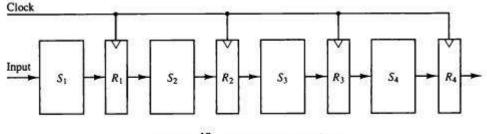

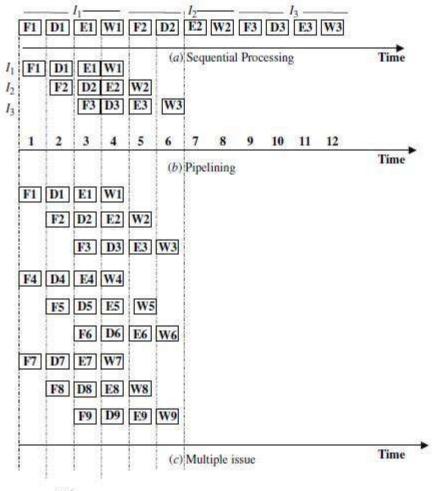

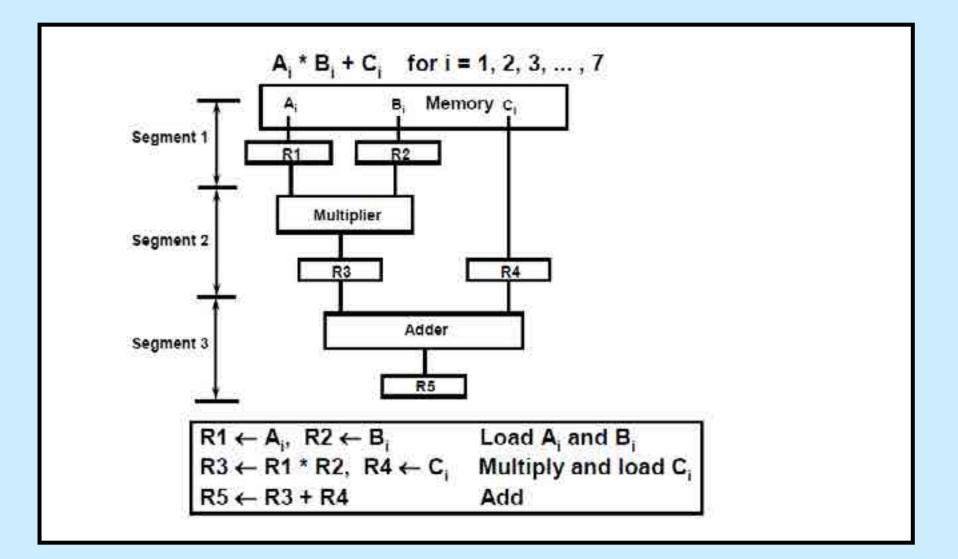

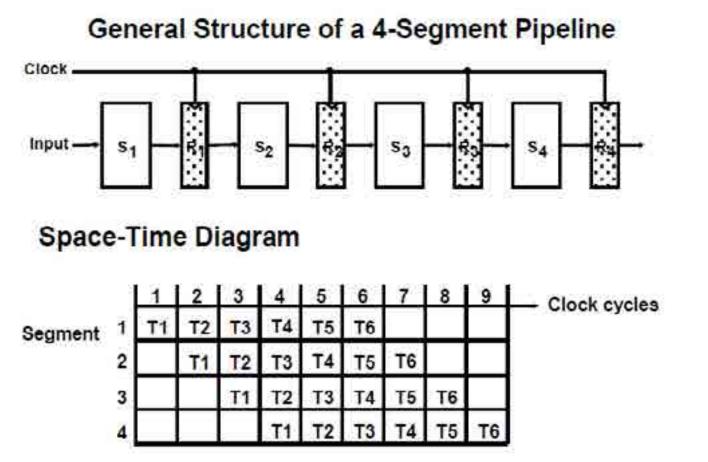

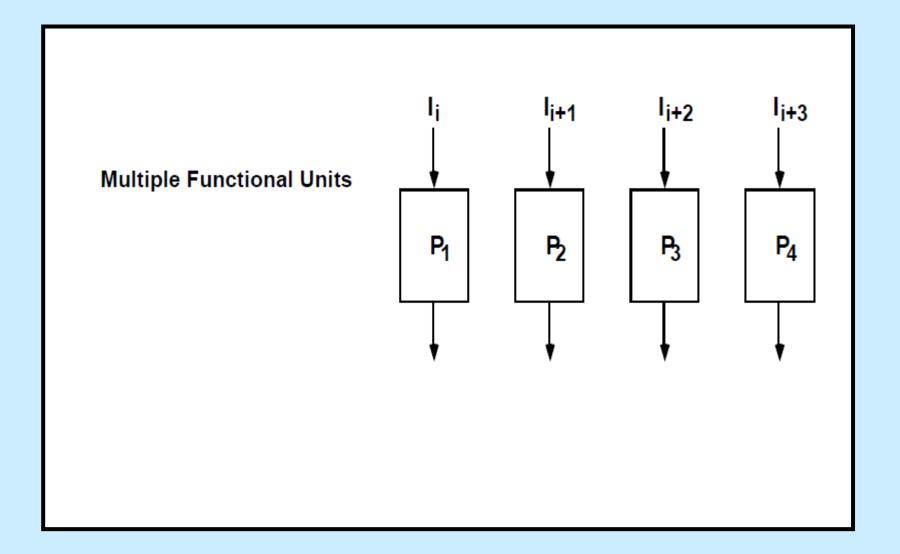

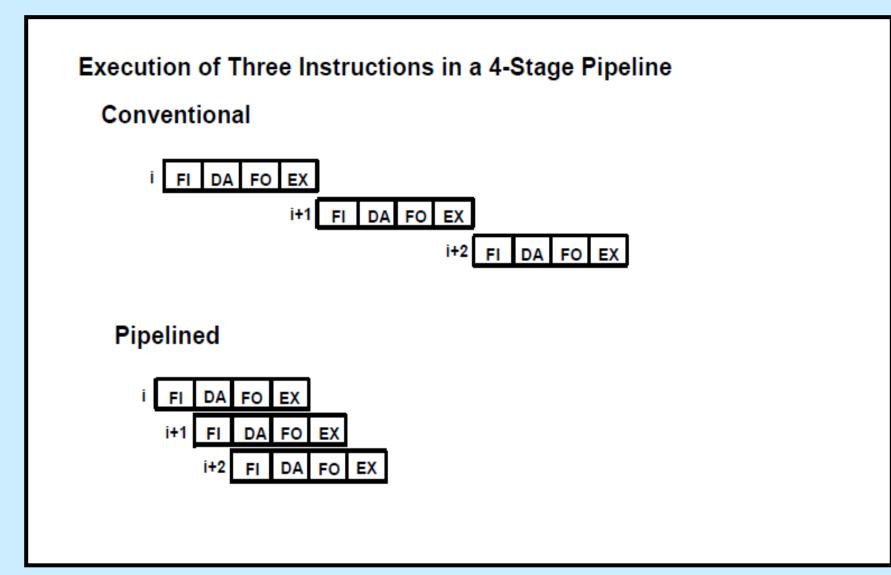

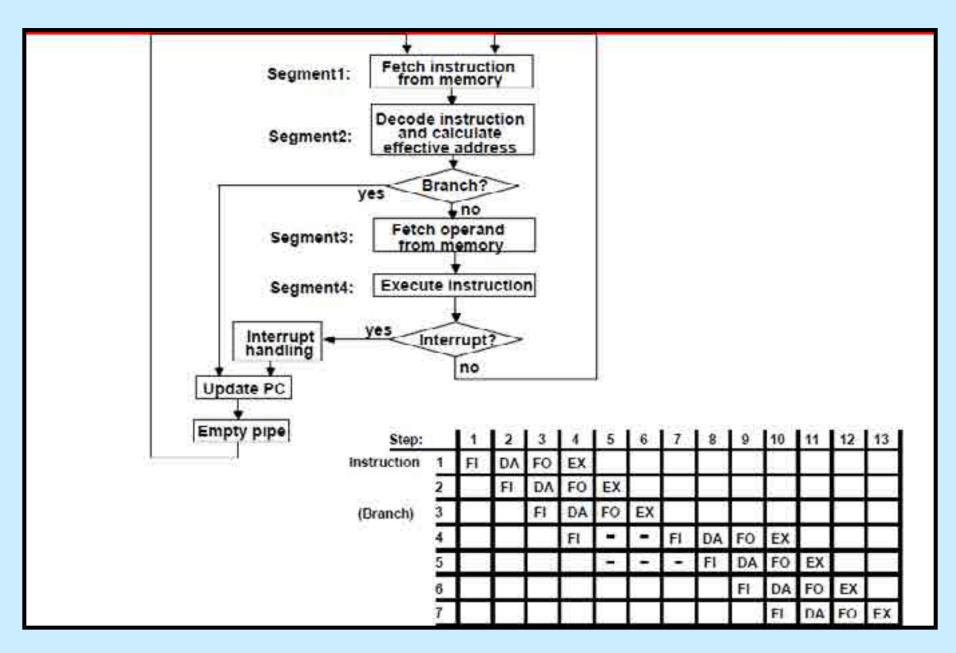

- Pipeline (general consideration).

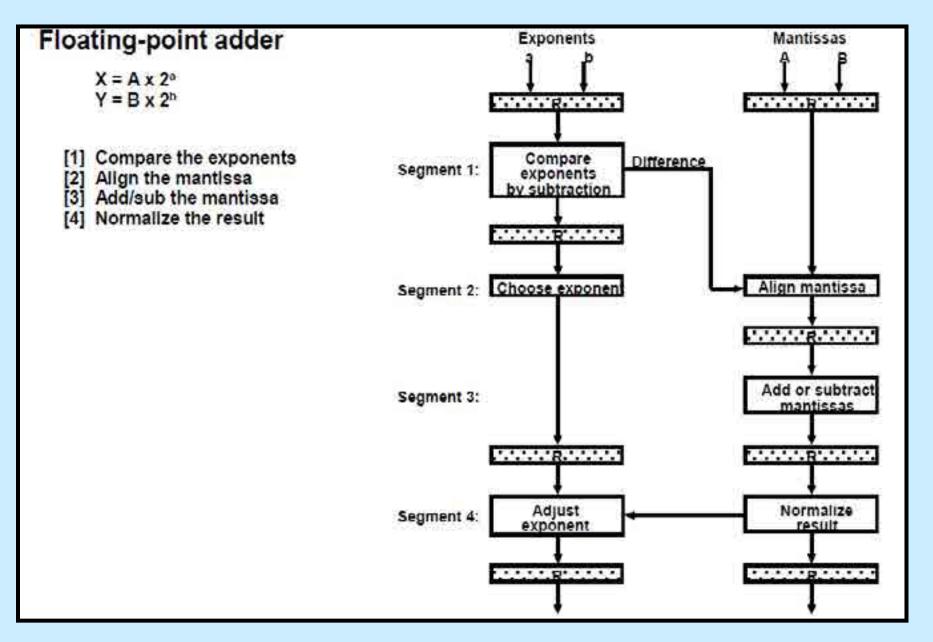

- Arithmetic Pipeline.

- Instruction Pipeline.

- Difficulties and Solutions in Instruction Pipeline.

- Vector processing and Array Processing.

# 1. Introduction

Computer architecture is the organization of the components which make up a computer system and the meaning of the operations which guide its function. It defines what is seen on the machine interface, which is targeted by programming languages and their compilers.

# Q1: \ What is computer architecture?

**Computer architecture** can be defined as a set of rules and methods that describe the functionality, management and implementation of computers. To be precise, it is nothing but rules by which a system performs and operates.

# Computer Architecture can be divided into mainly three categories, which are as follows -

- Instruction set Architecture or ISA Whenever an instruction is given to processor, its role is to read and act accordingly. It allocates memory to instructions and also acts upon memory address mode (Direct Addressing mode or Indirect Addressing mode).

- Micro Architecture It describes how a particular processor will handle and implement instructions from ISA.

- System design It includes the other entire hardware component within the system such as virtualization, multiprocessing.

### **Role of computer Architecture**

The main role of Computer Architecture is to balance the performance, efficiency, cost and reliability of a computer system.

**For Example** – Instruction set architecture (ISA) acts as a bridge between computer's software and hardware. It works as a programmer's view of a machine.

Computers can only understand binary language (i.e., 0, 1) and users understand high level language (i.e., if else, while, conditions, etc). So to communicate between user and computer, Instruction set Architecture plays a major role here, translating high level language to binary language.

# **Structure Computer Architecture**

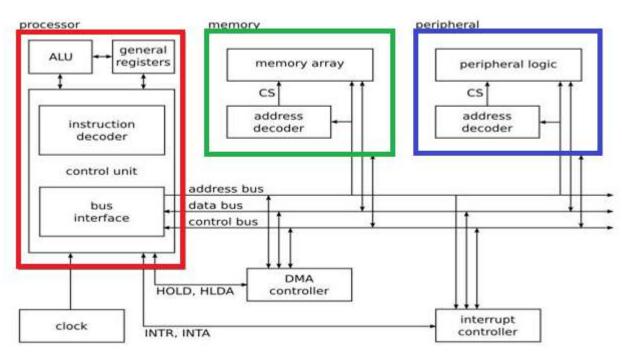

Example structure of Computer Architecture as given below. Generally, computer architecture consists of the following –

- Processor

- Memory

- Peripherals

All the above parts are connected with the help of system bus, which consists of **address bus**, **data bus** and **control bus**.

The diagram given below depicts the computer architecture -

# **1.1. RISC and CISC Architecture**

Means classification of instructions set to categories to increase the performance of Computer (Classification Instruction Set According Languages program)

# 1. <u>Reduced Instruction Set Computer (RISC)</u>

An important aspect of computer architecture is the design of the instruction set for the processor. The instruction set chosen for a particular computer determines the way that machine language programs are constructed. A computer with a large number of instructions is classified as a complex instruction set computer, abbreviated CISC. In the early 1980s, a

# **Reduced Instruction Set Computer or RISC Architecture**

The fundamental goal of RISC is to make hardware simpler by employing an instruction set that consists of only a few basic steps used for evaluating, loading, and storing operations. A load command loads data but a store command stores data.

### Characteristics of RISC:

- 1. It has simpler instructions and thus simple instruction decoding.

- 2. More general-purpose registers.

- 3. The instruction takes one clock cycle in order to get executed.

- 4. The instruction comes under the size of a single word.

- 5. Pipeline can be easily achieved.

- 6. Few data types.

- 7. Simpler addressing modes.

# 2. Complex Instruction Set Computer or CISC Architecture

The fundamental goal of CISC is that a single instruction will handle all evaluating, loading, and storing operations, similar to how a multiplication command will handle evaluating, loading, and storing data, which is why it's complicated.

# Characteristics of CISC:

- 1. Instructions are complex, and thus it has complex instruction decoding.

- 2. The instructions may take more than one clock cycle in order to get executed.

- 3. The instruction is larger than one-word size.

- 4. Lesser general-purpose registers since the operations get performed only in the memory.

- 5. More data types.

- 6. Complex addressing modes.

Both CISC and RISC approaches primarily try to increase the performance of a CPU. Here is how both of these work:

**1. CISC:** This kind of approach tries to minimize the total number of instructions per program, and it does so at the cost of increasing the total number of cycles per instruction.

**2. RISC:** It reduces the cycles per instruction and does so at the cost of the total number of instructions per program.

When

programming was done in assembly language earlier, there was a desire to make the instructions perform more tasks. It is because assembly programming was arduous (شاق) and error-prone (معرض الخطأ) and led to the evolution of CISC architecture. But as the dependency of high-level language on assembly language decreased, RISC architecture prevailed (هو السائد).

#### Example

Suppose we need to add two different 8-bit numbers:

**1. CISC approach:** There would be a single instruction or command for this, such as ADD, that would perform the task.

**2. RISC approach:** In this case, the programmer would write the very first load command in order to load data in the registers. Then it would use a suitable operator and store the obtained result in the location that is desired.

The add operation here is divided into parts, namely, **operate**, **load**, **and store**. Due to this, RISC programs are much longer, and they require more memory to get stored, even though they require fewer transistors because the commands are less complex.

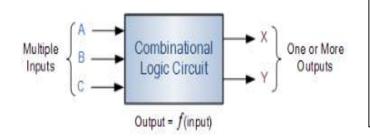

# Q1: \ What is combinational circuit?

In digital electronics, a combinational circuit is a circuit in which the output depends on the present combination of inputs. Combinational circuits are made up of logic gates. The output of each logic gate is determined by its logic function.

# Q2: What is difference between combinational and sequential circuit?

- 1. **combinational circuit** is time-independent. The output it generates does not depend on any of its previous inputs.

- 2. **sequential circuits** are the ones that depend on clock cycles. They depend entirely on the past as well as the present inputs for generating output.

| Parameters                | Combinational Circuit                                                                                                                                                       | Sequential Circuit                                                                                                                                                                                                                                                                                     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Meaning and<br>Definition | It is a type of circuit that<br>generates an output by relying on<br>the input it receives at that<br>instant, and it stays independent<br>of time.                         | It is a type of circuit in which the output does<br>not only rely on the current input. It also relies<br>on the previous ones.                                                                                                                                                                        |

| Feedback                  | A Combinational Circuit requires<br>no feedback for generating the<br>next output. It is because its<br>output has no dependency on the<br>time instance.                   | The output of a Sequential Circuit, on the other<br>hand, relies on both- the previous feedback and<br>the current input. So, the output generated from<br>the previous inputs gets transferred in the form<br>of feedback. The circuit uses it (along with<br>inputs) for generating the next output. |

| Performance               | We require the input of only the<br>current state for a Combinational<br>Circuit. Thus, it performs much<br>faster and better in comparison<br>with the Sequential Circuit. | In the case of a Sequential Circuit, the<br>performance is very slow and also<br>comparatively lower. Its dependency on the<br>previous inputs makes the process much more<br>complex.                                                                                                                 |

| Complexity                | It is very less complex in<br>comparison. It is because it<br>basically lacks implementation of<br>feedback.                                                                | This type of circuit is always more complex in<br>its nature and functionality. It is because it<br>implements the feedback, depends on previous<br>inputs and also on clocks.                                                                                                                         |

| Elementary<br>Blocks      | Logic gates form the building/<br>elementary blocks of a<br>Combinational Circuit.                                                                                          | Flip-flops form the building/ elementary blocks<br>of a Sequential Circuit.                                                                                                                                                                                                                            |

| Operation                 | One can use these types of<br>circuits for both- Boolean as well<br>as Arithmetic operations.                                                                               | You can mainly make use of these types of<br>circuits for storing data.                                                                                                                                                                                                                                |

| Combinational Logic Circuits                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Combinational Logic Circuits are<br>memoryless digital logic circuits<br>whose output at any instant in time<br>depends only on the combination of<br>its inputs. |

| ns inputs.                                                                                                                                                        |

Unlike Sequential Logic Circuits whose outputs are dependent on both their present inputs and their previous output state giving them some form of *Memory*.

The outputs of **Combinational Logic Circuits** are only determined by the logical function of their current input state, logic "0" or logic "1", at any given instant in time.

Q4: \ You have Three digital inputs (A, B, C) and output (Q), Design Combinational Logic Circuits (your Answer should appear (Logical diagram, Boolean Expression and Typical truth table)? Solution

# **Q1:** \ What are the differences between Combinational circuitry and State circuitry? Solution

- 1. <u>**Combinational circuitry**</u> behaves like a simple function. The output of combinational circuitry depends only on the current values of its input.

- 2. <u>State circuitry</u> behaves more like an object method. The output of state circuitry does not just depend on its inputs it also depends on the past history of its inputs.

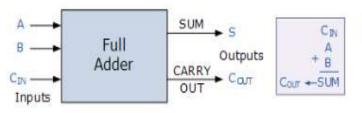

# Q2: \What is the Difference Between Half Adder and Full Adder? **Solution**

There is a primary difference between half adder and full adder. Half adder only adds the current inputs as 1-bit numbers and does not focus on the previous inputs. On the other hand, Full Adder can easily carry the current inputs as well as the output from the previous additions.

# What is a Half Adder?

It is a combinational logic circuit. You can design it by connecting one AND gate and one EX-OR gate. A half-adder circuit consists of two input terminals- namely A and B. Both of these add two input digits (onebit numbers) and generate the output in the form of a **carry and a sum**. Thus, there are two output terminals.

The output that one obtains from the EX-OR gate is the sum of both the one-bit numbers. The output obtained from the AND gate is called the carry. But you cannot forward the carry that you obtain in one addition into another addition. It is because of the absence of any logic gate to process it. Thus, it's called the Half Adder circuit.

We can write the equation of output for both the gates in the form of a logical operation that the logic gates perform. Here, we write the carry equation in the form of AND operation and the sum equation in the form of EX-OR operation.

Logical Expression of Half Adder

$\mathbf{Sum}\,(\mathbf{S}) = \mathbf{A} \bigoplus \mathbf{B}$

Carry (C) =  $A \bullet B$

#### Truth Table

Here is a truth table representing the possible outputs obtained from the possible inputs in a Half Adder:

| Input |   | Output |     |  |  |  |

|-------|---|--------|-----|--|--|--|

| А     | в | CARRY  | SUM |  |  |  |

| 0     | 0 | 0      | 0   |  |  |  |

| 1     | 1 | 1      | 0   |  |  |  |

| 0     | 1 | 0      | 1   |  |  |  |

| 1     | 0 | 0      | 1   |  |  |  |

# What is Full Adder?

A full adder is a circuit that has two AND gates, two EX-OR gates, and one OR gate. The full adder adds three binary digits. Among all the three, one is the carry that we obtain from the previous addition as C-IN, and the two are inputs A and B. It designates the input carry as the C-OUT and the normal output as S (or SUM).

Just like the Half Adder, the Full Ladder is a combinational type of logic circuit- meaning, it has no storage element. But it has additional logic gates. Thus, it adds the previous carry to generate the complete output. Thus, it is called the Full Adder.

One can also designate a Full Adder using one OR gate and two Half Adders. The OR gate here generates a carry that it obtains after the addition. We obtain the sum of these digits in the form of output from the second Half Adder.

The equation for the output that you can obtain by the EX-OR gate is the sum of all the binary digits. Here, the output that you obtain from the AND gate is the carry that you obtain by addition. This equation is in the form of a logical operation.

#### Logical Expression of Full Adder

$CARRY-OUT = AB + BCin \bigoplus ACin$

#### $SUM = (A \bigoplus B) \bigoplus Cin$

#### Truth Table

A truth table represents the possible outputs obtained from the possible inputs. A truth table for the Full Adder is as follows:

| Input |   |   | Output |           |  |

|-------|---|---|--------|-----------|--|

| A     | В | С | SUM    | CARRY OUT |  |

| 0     | 0 | 0 | 0      | 0         |  |

| 1     | 1 | 1 | 1      | 1         |  |

| 0     | 1 | 1 | 0      | 1         |  |

| 1     | 0 | 1 | 0      | 1         |  |

| 0     | 0 | 1 | ٦      | o         |  |

| 0     | 1 | 0 | 1      | 0         |  |

| 1     | 0 | 0 | 1      | 0         |  |

| 1     | 1 | 0 | 0      | 1         |  |

# Q:\What are the main difference between <u>Half Adder</u> and <u>Full Adder</u>? Solution

| Parameter                    | Half Adder                                                                                                                                                   | Full Adder                                                                                                                                                                                                          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basics                       | The Half Adder is a type of<br>combinational logic circuit that<br>adds two of the 1-bit binary digits. It<br>generates carry and sum of both the<br>inputs. | The Full Adder is also a type of<br>combinational logic that adds three of the 1-<br>bit binary digits for performing an addition<br>operation. It generates a sum of all three<br>inputs along with a carry value. |

| Adding the<br>Previous Carry | The Half Adder does not add the<br>carry obtained from the previous<br>addition to the next one.                                                             | The Full Adder, along with its current inputs A<br>and B, also adds the previous carry.                                                                                                                             |

| Hardware<br>Architecture     | A Half Adder consists of only one AND gate and EX-OR gate.                                                                                                   | A Full Adder consists of one OR gate and two<br>EX-OR and AND gates.                                                                                                                                                |

| Total Inputs                 | There are two inputs in a Half<br>Adder- A and B.                                                                                                            | There are a total of three inputs in a Full<br>Adder- A. B. C-in.                                                                                                                                                   |

| Usage                        | The Half Adder is good for digital<br>measuring devices, computers,<br>calculators, and many more.                                                           | The Full Adder comes into play in various digital processors, the addition of multiple bits, and many more.                                                                                                         |

| Logical<br>Expression        | Here is the logical expression of<br>Half Adder:<br>C = A * B<br>$S = A \oplus B$                                                                            | Here is the logical expression of Full Adder:<br>Cout = (AB) + CinA $\oplus$ CinB<br>S = A $\oplus$ B $\oplus$ Cin                                                                                                  |

# Q6: What Means by multiplexer?

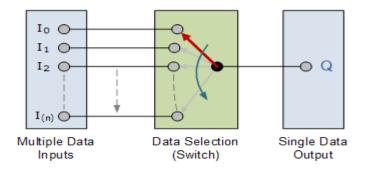

Multiplexing is the generic term used to describe the operation of sending one or more analogue or digital signals over a common transmission line at **different times** or **speeds** and as such, the device we use to do just that is called the multiplexer.

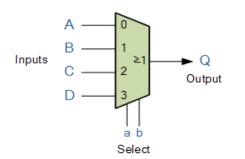

The *multiplexer*, shortened to "MUX" or "MPX", is a combinational logic circuit designed to switch one of several input lines through to a single common output line by the application of a control signal. Multiplexers operate like very fast acting multiple position rotary switches connecting or controlling multiple input lines called "channels" one at a time to the output.

# The Multiplexer

The multiplexer is a combinational logic circuit designed to switch one of several input lines to a single common output line

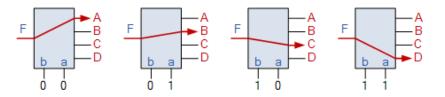

A. Basic multiplexing Switch

### B. 2- multiplexing Switch

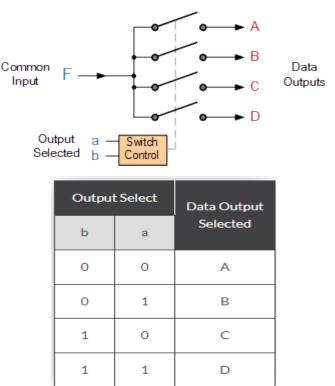

### **Q7: What Means by Demultiplexer**

# The Demultiplexer

The demultiplexer is a combinational logic circuit designed to switch one common input line to one of several seperate output line

The data distributor, known more commonly as the demultiplexer or "Demux" for short, is the exact opposite of the Multiplexer we saw in the previous tutorial.

The *demultiplexer* takes one single input data line and then switches it to any one of a number of individual output lines one at a time. The **demultiplexer** converts a serial data signal at the input to a parallel data at its output lines as shown below.

The Boolean expression for this 1-to-4 **Demultiplexer** above with outputs A to D and data select lines a, b is given as:

$$F = \overline{ab}A + \overline{ab}B + \overline{ab}C + \overline{ab}D$$

The function of the **Demultiplexer** is to switch one common data input line to any one of the 4 output data lines A to D in our example above. As with the multiplexer the individua solid state switches are selected by the binary input address code on the output select pins "a" and "b" as shown.

# **Demultiplexer Output Line Selection**

As with the previous multiplexer circuit, adding more address line inputs it is possible to switch more outputs giving a 1-to-2<sup>n</sup> data line outputs.

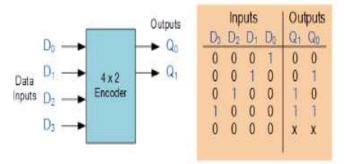

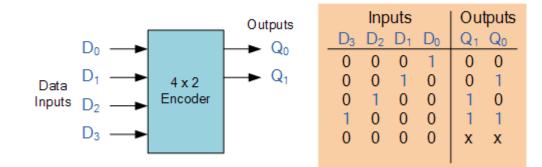

# **Q8: What Means by Priority Encoder**

# **Priority Encoder**

Priority Encoders take all of their data inputs one at a time and converts them into an equivalent binary code at its output

Unlike a multiplexer that selects one individual data input line and then sends that data to a single output line or switch. The job of a priority encoder is to produce a binary output address for the input with the highest priority.

The **Digital Encoder** more commonly called a **Binary Encoder** takes ALL its data inputs one at a time and then converts them into a single encoded output. So we can say that a binary encoder, is a multi-input combinational logic circuit that converts the logic level "1" data at its inputs into an equivalent binary code at its output.

Generally, digital encoders produce outputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines. An "n-bit" binary encoder has 2<sup>n</sup> input lines and n-bit output lines with common types that include 4-to-2, 8-to-3 and 16-to-4 line configurations.

# Example:

# 4-to-2 Bit Binary Encoder

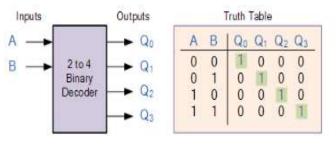

# **Q9: What Means by Binary Decoder?**

# **Binary Decoder**

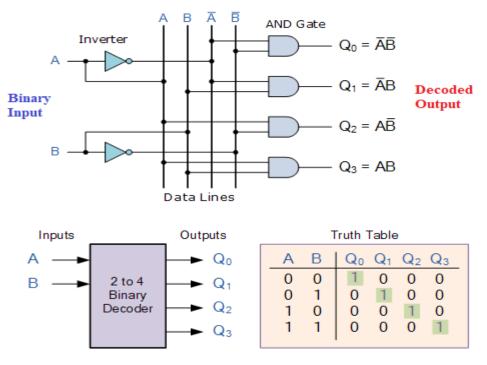

Binary Decoder is another combinational logic circuit constructed from individual logic gates and is the exact opposite to that of an Encoder

The term "**Decoder**" means to translate or decode coded information from one format into another, so a binary decoder transforms "n" binary input signals into an equivalent code using  $2^n$  outputs.

**Binary Decoders** are another type of digital logic device that has inputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines, so a decoder that has a set of two or more bits will be defined as having an *n*-bit code, and therefore it will be possible to represent  $2^n$  possible values. Thus, a decoder generally decodes a binary value into a non-binary one by setting exactly one of its *n* outputs to logic "1".

# Example: A 2-to-4 Binary Decoders

# **Q10: What Means by Binary Adder?**

# **Binary Adder**

Binary Adders are arithmetic circuits in the form of half-adders and full-adders be used to add together two binary digits

Another common and very useful combinational logic circuit which can be constructed using just a few basic logic gates allowing it to add together two or more binary numbers is the **Binary Adder**.

A basic Binary Adder circuit can be made from standard AND and Ex-OR gates allowing us to "add" together two single bit binary numbers, A and B.

The addition of these two digits produces an output called the SUM of the addition and a second output called the CARRY or Carry-out, (Cour) bit according to the rules for binary addition. One of the main uses for the *Binary Adder* is in arithmetic and counting circuits. Consider the simple addition of the two denary (base 10) numbers and Binary Addition of two bits below.

| Decimal | Addition |          |           | Binary Ac | ldition of | Two Bits    |

|---------|----------|----------|-----------|-----------|------------|-------------|

| 123     | A        |          | 0         | 0         | 1          | 1           |

| + 789   | B        | (Addend) | <u>+0</u> | <u>+1</u> | <u>+0</u>  | <u>+ 1</u>  |

| 912     | SUM      |          | 0         | 1         | 1          | (carry) 1←0 |

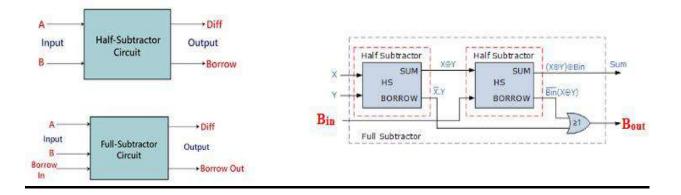

# **Q11: What Means by Binary Subtractor?**

The Binary Subtractor is another type of combinational arithmetic circuit that produces an output which is the subtraction of two binary numbers.

As their name implies, a **Binary Subtractor** is a decision making circuit that subtracts two binary numbers from each other, for example, X - Y to find the resulting difference between the two numbers.

Unlike the Binary Adder which produces a SUM and a CARRY bit when two binary numbers are added together, the *binary subtractor* produces a DIFFERENCE, D by using a BORROW bit, B from the previous column. Then obviously, the operation of subtraction is the opposite to that of addition

# COMPUTER ARCHITECTURE

#### **Digital Computer**

The digital computer is a digital system that performs various computational tasks. Digital computers use the binary number system, which has two digits: 0 and 1. A binary digit is called a bit. Information is represented in digital computers in groups of bits. By using various coding techniques, groups of bits can be made to represent not only binary numbers but also other discrete symbols, such as decimal digits or letters of the alphabet. By judicious use of binary arrangements and by using various coding techniques, the groups of bits are used to develop complete sets of instructions for performing various types of computations.

A computer system is sometimes subdivided into two functional entities

- 1- The hardware of the computer consists of all the electronic components and electromechanical devices that comprise the physical entity of the device.

- 2- Computer software consists of the instructions and data that the computer manipulates to perform various data-processing tasks.

The system software of a computer consists of a collection of programs whose purpose is to make more effective use of the computer. The programs included in a systems software package are referred to as the operating system.

#### **Computer Hardware**

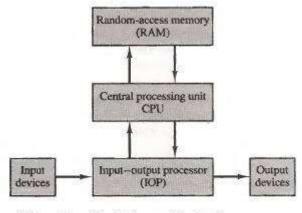

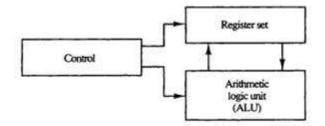

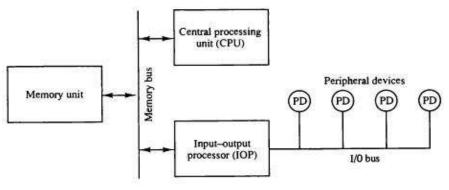

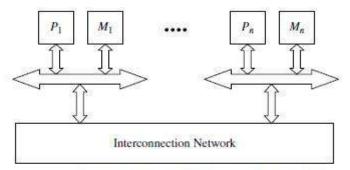

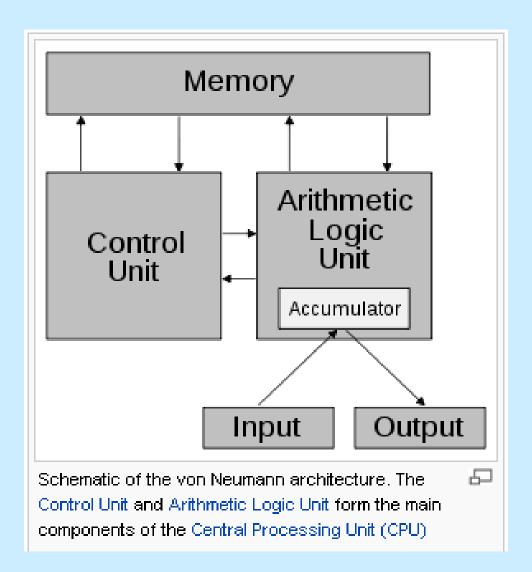

The hardware of the computer is usually divided into three major parts, as shown in Fig(1):

Figure 1 Block diagram of a digital computer.

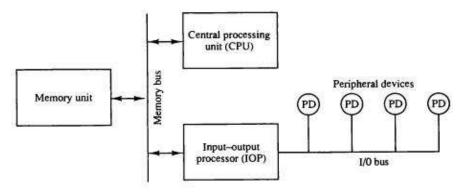

The central processing unit (CPU) contains arithmetic and logic unit for manipulating data, a number of registers for storing data, and control circuits for fetching and executing instructions. The memory of a computer contains storage for instructions and data. It is called a random- access memory (RAM) because the CPU can access any location in memory at random and retrieve the binary information within a fixed interval of time. The input and output processor (IOP) contains electronic circuits for communicating and controlling the transfer of information between the computer and the outside world. The input and output devices connected to the computer include keyboards, printers, terminals, magnetic disk drives, and other communication devices.

### **Computer Organization**

Computer organization is concerned with the way the hardware components operate and the way they are connected together to form the computer system. The various components are assumed to be in place and the task is to investigate the organizational structure to verify that the computer parts operate as intended.

#### Computer Design

Computer design is concerned with the hardware design of the computer. Once the computer specifications are formulated, it is the task of the designer to develop hardware for the system. Computer design is concerned with the determination of what hardware should be used and how the parts should be connected. This aspect of computer hardware is sometimes referred to as computer implementation.

#### **Computer Architecture**

Computer architecture is concerned with the structure and behavior of the computer as seen by the user. It includes the information formats, the instruction set, and techniques for addressing memory. The architectural design of a computer system is concerned with the specifications of the various functional modules, such as processors and memories, and structuring them together into a computer system.

# **Instruction Set Architecture**

- 1. **Opcodes**: Consists of operate instructions: as logical and arithmetical instructions, Data movement instructions and Control instructions

- 2. Data types: consists of 8, 16, 32, and 64 bits

- 3. Addressing modes: consists of:

- Operands specified

- Next instruction to execute is specified

- Architecture-specific

- An instruction can use several addressing modes

# **Register Transfer Language**

Digital systems vary in size and complexity from a few integrated circuits to a complex of interconnected and interacting digital computers. Digital system design invariably uses a modular approach(نهج معياري او نهج نمطي). The modules are constructed from such digital components as registers, decoders, arithmetic elements, and control logic. The various modules are interconnected with common data and control paths to form a digital computer system.

Digital modules are best defined by the registers they contain and the operations that are performed on the data stored in them. The operations executed on data stored in registers are called micro operations(MO).

A micro operation is an elementary operation (عملية ابتدائية) performed on the information stored in one or more registers. The result of the operation may replace the previous binary information of a register or may be transferred to another register. Examples of micro operations are shift, count, dear, and load.

The internal hardware organization of a digital computer is best defined by specifying:

- 1- The set of registers it contains and their function.

- 2- The sequence of micro operations performed on the binary information stored in the registers.

- 3- The control that initiates the sequence of micro operations.

The symbolic notation used to describe the micro operation transfers among registers is called a *register transfer language*.

The term "register transfer" implies the availability of hardware logic circuits that can perform a stated micro operation and transfer the result of the operation to the same or another register.

The word "language" is borrowed from programmers, who apply this term to programming languages.

A *register transfer language* is a system for expressing in symbolic form the micro operation sequences among the registers of a digital module.

# **Register Transfer**

Computer registers are designated (يعين) by capital letters (sometimes followed by numerals) to denote the function of the register.

For example:

MAR: memory address register

PC: program counter

IR: instruction register

R1: processor register

The representation of registers in block diagram form is shown in Fig(2):

Figure 2 Block diagram of register.

- a- Rectangular box with the name of the register inside.

- b- The individual bits.

- c- The numbering of bits in a 16-bit register can be marked on top of the box. d- 16-bit register is partitioned into two parts. Bits 0 through 7 are assigned the symbol L (for low byte) and bits 8 through 15 are assigned the symbol H (for high byte).

- d- The name of the 16-bit register is PC. The symbol PC (0-7) or PC(L) refers to the loworder byte and PC (8-15) or PC(H) to the high-order byte. Information transfer from one register to another is designated in symbolic form by means of a *replacement* operator. The statement:

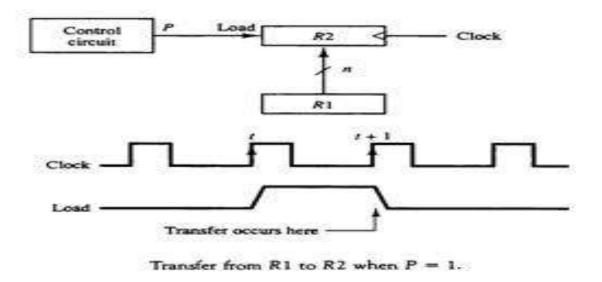

# $R2 \leftarrow R1$

Denotes a transfer of the content of register Rl into register R2. It designates a replacement of the content of R2 by the content of R1. By definition, the content of the source register Rl does not change after the transfer.

If we want the transfer to occur only under a predetermined control condition. This can be shown by means of an if-then statement.

If

$$(P = 1)$$

then  $(R2 \leftarrow R1)$

where P is a control signal generated in the control section. It is sometimes convenient

to separate the control variables from the register transfer operation control function by specifying a control function. (من الملائم أحيانًا فصل متغيرات التحكم عن وظيفة التحكم في عملية نقل السجل من خلال تحديد وظيفة التحكم.)

$P: R2 \leftarrow R1$

The control condition is terminated with a colon. It symbolizes (برمز) the requirement that the transfer operation be executed by the hardware only if P = 1.

To separate two or more operations that is executed at the same time by using the *comma* as the statement:

$$T: R2 \leftarrow R1, R5 \leftarrow R3$$

The basic symbols of the register transfer notation are listed in Table (1) Registers are denoted by capital letters, and numerals may follow the letters. Parentheses are used to denote a part of a register by specifying the range of bits or by giving a symbol name to a portion of a register.

TABLE 1 Basic Symbols for Register Transfers

| Symbol                    | Description                     | Examples                             |

|---------------------------|---------------------------------|--------------------------------------|

| Letters<br>(and numerals) | Denotes a register              | MAR, R2                              |

| Parentheses ( )           | Denotes a part of a register    | R2(0-7), R2(L)                       |

| Arrow ←                   | Denotes transfer of information | $R2 \leftarrow R1$                   |

| Comma,                    | Separates two microoperations   | $R2 \leftarrow R1, R1 \leftarrow R2$ |

# **Bus and Memory Transfers**

A typical digital computer has many registers, and paths must be provided to transfer information from one register to another. The number of wires will be excessive (مُبَالَغ فيه) if separate lines are used between each register and all other registers in the system.

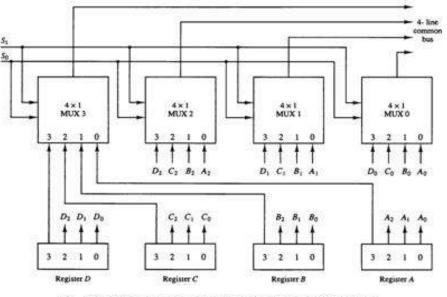

A bus structure consists of a set of common lines, one for each bit of a register, through which binary information is transferred one at a time. Control signals determine which register is selected by the bus during each particular register transfer. The multiplexers select the source register whose binary information is then placed on the bus. For example, the construction of a bus system for four registers is shown in Fig (3) Each register has four bits, numbered 0 through 3. The bus consists of four 4x1(4-input-one output) multiplexers each having four data inputs, 0 through 3, and two selection inputs, S1 and S0. (00,01,10,11)

Fig 3 Bus system for four registers

The table (2) shows the register that is selected by the bus for each of the four possible binary values of the selection lines.

| Ta                    | Table 2 Function for Bus of Fig |                   |  |  |  |  |  |

|-----------------------|---------------------------------|-------------------|--|--|--|--|--|

| <i>S</i> <sub>1</sub> | So                              | Register selected |  |  |  |  |  |

| 0                     | 0                               | Α                 |  |  |  |  |  |

| 0                     | 1                               | В                 |  |  |  |  |  |

| 1                     | 0                               | С                 |  |  |  |  |  |

| 1                     | 1                               | D                 |  |  |  |  |  |

The symbolic statement for a bus transfer may mention the bus or its presence may be implied in the statement. When the bus is including in the statement, the register transfer is symbolized as follows:

### $Bus \leftarrow C$ , $R1 \leftarrow Bus$

The content of register C is placed on the bus, and the content of the bus is loaded into register Rl by activating its load control input. If the bus is known to exist in the system, it may be convenient just to show the direct transfer.

$$R1 \leftarrow C$$

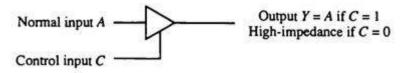

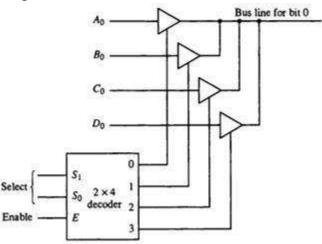

A bus system can be constructed with three-state gates. The graphic symbol of a three state buffer gate is shown:

Graphic symbols for three-state buffer.

To construct a common bus for four registers of n bits each using three-state buffers, we need n circuits with four buffers in each as shown in Fig (4). Each group of four buffers receives one significant bit from the four registers.

Figure 4 Bus line with three state-buffers.

The transfer of information from a memory word to the outside environment is called a read operation. The transfer of new information to be stored into the memory is called a write operation. Consider a memory unit that receives the address from a register, called the Address Register, symbolized by **AR**. The data are transferred to another register, called the Data Register, symbolized by DR.

# *Read*: $DR \leftarrow M[AR]$

The write operation transfers the content of a data register to a memory word M selected by the address.

Write:

$$M[AR] \leftarrow DR$$

# **Arithmetic Microoperations**

The arithmetic operations are listed in the Table(3):

| Symbolic designation                   | Description                                    |  |  |  |  |  |

|----------------------------------------|------------------------------------------------|--|--|--|--|--|

| $R3 \leftarrow R1 + R2$                | Contents of R1 plus R2 transferred to R3       |  |  |  |  |  |

| $R3 \leftarrow R1 - R2$                | Contents of R1 minus R2 transferred to R3      |  |  |  |  |  |

| $R2 \leftarrow \overline{R2}$          | Complement the contents of R2 (1's complement) |  |  |  |  |  |

| $R2 \leftarrow \overline{R2} + 1$      | 2's complement the contents of R2 (negate)     |  |  |  |  |  |

| $R3 \leftarrow R1 + \overline{R2} + 1$ | R1 plus the 2's complement of R2 (subtraction) |  |  |  |  |  |

| $R1 \leftarrow R1 + 1$                 | Increment the contents of R1 by one            |  |  |  |  |  |

| $R1 \leftarrow R1 - 1$                 | Decrement the contents of R1 by one            |  |  |  |  |  |

TABLE 3 Arithmetic Microoperations

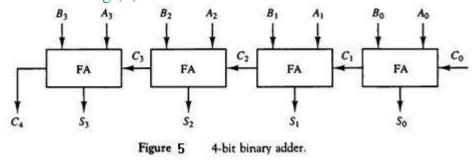

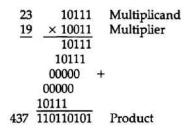

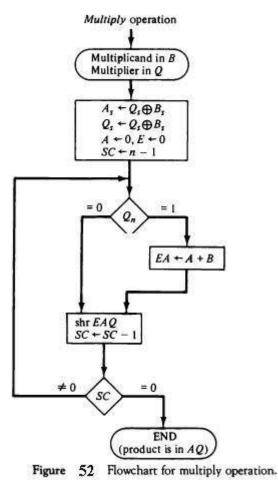

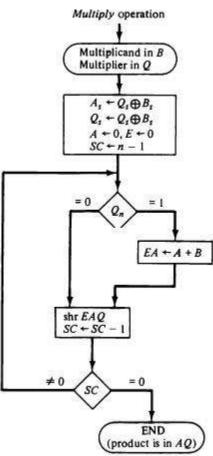

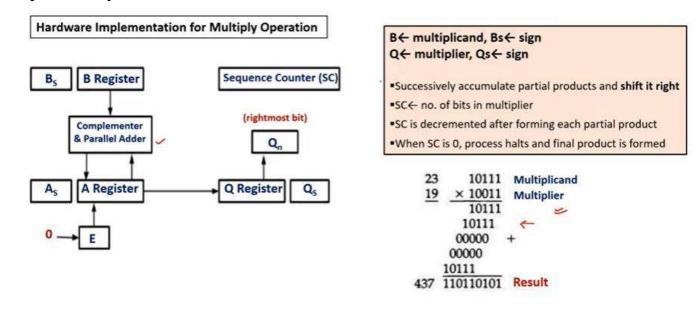

The multiply and divide are not listed in Table (3), these two operations are valid arithmetic operations but are not included in the basic set of micro operations. In most computers, the multiplication operation is implemented with a sequence of add and shift micro operations. Division is implemented with a sequence of subtract and shift micro operations. The digital circuit that generates the arithmetic sum of two binary numbers of any length is called a binary adder as shown in Fig (5).

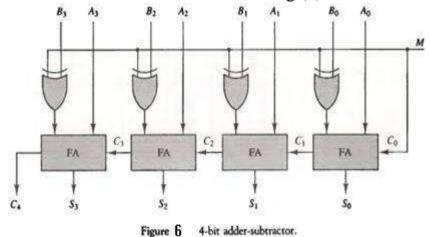

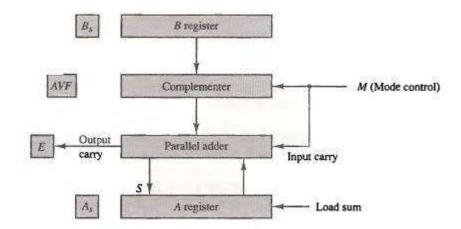

The *addition and subtraction operations* can be combined into one common circuit by including an exclusive-OR gate with each full-adder as shown in Fig (6).

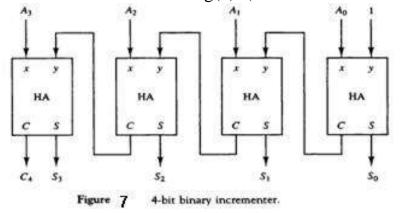

The increment micro operation adds one to a number in a register. For example, if a 4-bit register has a binary value 0110, it will go to 0111 after it is incremented. The diagram of a 4bit combinational circuit incremented is shown in Fig(7): (HA means Half Adder)

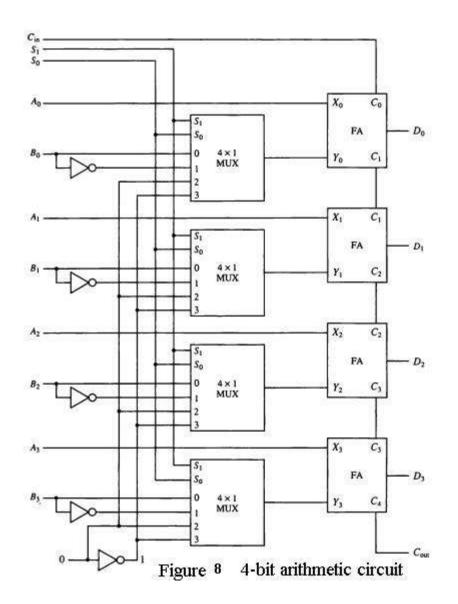

The arithmetic micro operations listed in the Table 3 can be implemented in one composite arithmetic circuit. The basic component of an arithmetic circuit is the parallel adder. By controlling the data inputs to the adder, it is possible to obtain different types of arithmetic operations as shown in Fig (8).

It is possible to generate the eight arithmetic micro operations listed in Table (4): **TABLE 4** Arithmetic Circuit Function Table

| Select         |                | 2   | Input                    | Output                     |                      |

|----------------|----------------|-----|--------------------------|----------------------------|----------------------|

| S <sub>1</sub> | S <sub>0</sub> | Cin | Y                        | $D = A + Y + C_{\rm in}$   | Microoperation       |

| 0              | 0              | 0   | B                        | D = A + B                  | Add                  |

| 0              | 0              | 1   | B                        | D = A + B + 1              | Add with carry       |

| 0              | 1              | 0   | $\frac{B}{\overline{B}}$ | $D = A + \overline{B}$     | Subtract with borrow |

| 0              | 1              | 1   | $\overline{B}$           | $D = A + \overline{B} + 1$ | Subtract             |

| 1              | 0              | 0   | 0                        | D = A                      | Transfer A           |

| 1              | 0              | 1   | 0                        | D = A + 1                  | Increment A          |

| 1              | 1              | 0   | 1                        | D = A - 1                  | Decrement A          |

| 1              | 1              | 1   | 1                        | D = A                      | Transfer A           |

#### **Logic Micro Operations**

Logic micro operations specify binary operations for strings of bits stored in registers. These operations consider each bit of the register separately and treat them as binary variables. For example, the exclusive-OR micro operation with the contents of two registers Rl and R2 is symbolized by the statement:

$$P: R1 \leftarrow R1 \bigoplus R2$$

It specifies a logic micro operation to be executed on the individual bits of the registers provided that the control variable P = 1. As a numerical example, assume that each register has four bits. Let the content of Rl be 1010 and the content of R2 be 1100. The exclusive-OR micro operation stated above symbolizes the following logic computation:

| 1010 | Content of R1               |

|------|-----------------------------|

| 1100 | Content of R2               |

| 0110 | Content of R1 after $P = 1$ |

There are 16 different logic operations that can be performed with two binary variables. They can be determined from all possible truth tables obtained with two binary variables as shown in Table (5):

TABLE 5 Touch Tables for 16 Exections of Two Variables

|   | e cas |    | 11                    | TDLI                  | . <b>л</b> | mu                    | ur is | intes          | 101 1                 | oru                   | netio | ins cit         | Two                    | variat          | 1Cb |     |   |

|---|-------|----|-----------------------|-----------------------|------------|-----------------------|-------|----------------|-----------------------|-----------------------|-------|-----------------|------------------------|-----------------|-----|-----|---|

| x | y     | Fo | <i>F</i> <sub>1</sub> | <b>F</b> <sub>2</sub> | F,         | <i>F</i> <sub>4</sub> | Fs    | F <sub>6</sub> | <i>F</i> <sub>7</sub> | <i>F</i> <sub>8</sub> | F,    | F <sub>10</sub> | <i>F</i> <sub>11</sub> | F <sub>12</sub> | F13 | F14 | F |

| 0 | 0     | 0  | 0                     | 0                     | 0          | 0                     | 0     | 0              | 0                     | 1                     | 1     | 1               | 1                      | 1               | 1   | 1   | 1 |

| 0 | 1     | 0  | 0                     | 0                     | 0          | 1                     | 1     | 1              | 1                     | 0                     | 0     | 0               | 0                      | 1               | 1   | 1   | 1 |

| 1 | 0     | 0  | 0                     | 1                     | 1          | 0                     | 0     | 1              | 1                     | 0                     | 0     | 1               | 1                      | 0               | 0   | 1   | 1 |

| 1 | 1     | 0  | 1                     | 0                     | 1          | 0                     | 1     | 0              | 1                     | 0                     | 1     | 0               | 1                      | 0               | 1   | 0   | 1 |

The 16 Boolean functions of two variables x and y are expressed in algebraic form in the first column of Table (6):

| Boolean function      | Microoperation                       | Name                                    |

|-----------------------|--------------------------------------|-----------------------------------------|

| $F_0 = 0$             | <i>F</i> ← 0                         | Clear                                   |

| $F_1 = xy$            | $F \leftarrow A \land B$             | AND                                     |

| $F_2 = xy'$           | $F \leftarrow A \land \overline{B}$  |                                         |

| $F_3 = x$             | F←A                                  | Transfer A                              |

| $F_{4} = x'y$         | $F \leftarrow \overline{A} \land B$  |                                         |

| $F_5 = y$             | F←B                                  | Transfer B                              |

| $F_6 = x \oplus y$    | $F \leftarrow A \oplus B$            | Exclusive-OR                            |

| $F_7 = x + y$         | $F \leftarrow A \lor B$              | OR                                      |

| $F_8 = (x + y)'$      | $F \leftarrow \overline{A \lor B}$   | NOR                                     |

| $F_9 = (x \oplus y)'$ | $F \leftarrow \overline{A \oplus B}$ | Exclusive-NOR                           |

| $F_{10} = y'$         | F←B                                  | Complement B                            |

| $F_{11} = x + y'$     | $F \leftarrow A \lor \overline{B}$   | 100 00 00 00 00 00 00 00 00 00 00 00 00 |

| $F_{12} = x'$         | $F \leftarrow \overline{A}$          | Complement A                            |

| $F_{13} = x' + y$     | $F \leftarrow \overline{A} \lor B$   | 12                                      |

| $F_{1*} = (xy)'$      | $F \leftarrow \overline{A \land B}$  | NAND                                    |

| $F_{15} = 1$          | F ← all 1's                          | Set to all 1's                          |

TABLE 6 Sixteen Logic Microoperations

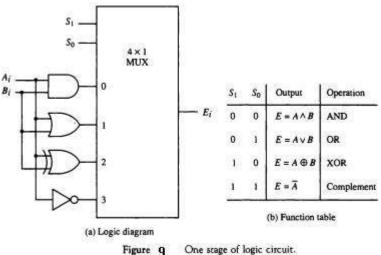

The diagram shows (Fig 9-a) one typical stage with subscript i. For a logic circuit with n bits, the diagram must be repeated n times for i = 0, 1, 2, ..., n - 1. The selection variables are applied to all stages. The function table in Fig.(9-b) lists the logic micro operations obtained for each combination of the selection variables.

Shift Micro operations

Shift micro operations are used for serial transfer of data. The contents of a register can be shifted to the left or the right. There are three types of shifts: logical, circular, and arithmetic. The symbolic notation for the shift micro operations is shown in Table (7):

TABLE 7 Shift Microoperations

| Symbolic designation                | Description                     |

|-------------------------------------|---------------------------------|

| R ← shl R                           | Shift-left register R           |

| $R \leftarrow \text{shr } R$        | Shift-right register R          |

| $R \leftarrow \text{cil } R$        | Circular shift-left register R  |

| $R \leftarrow \operatorname{cir} R$ | Circular shift-right register R |

| $R \leftarrow ashl R$               | Arithmetic shift-left R         |

| $R \leftarrow a shr R$              | Arithmetic shift-right R        |

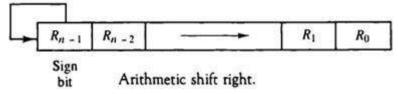

An arithmetic shift is a micro operation that shifts a signed binary number to the left or right. The arithmetic shift-left inserts a 0 into  $R_0$ , and shifts all other bits to the left. The initial bit of  $R_{n-1}$  is lost and replaced by the bit from  $R_{n-2}$ . A sign reversal occurs if the bit in  $R_{n-1}$  changes in value after the shift and caused an overflow.

The arithmetic shift-right leaves the sign bit unchanged and shifts the number (including the sign bit) to the right.

Ex: If the content of 8 bits register is (10100011). What is the result of the operation after executing to the register:

a. shl R: shift left register by 3. b. cil R : circular shift left register by 3.

c. ashl R: arithmetic shift left register by 3. d. ashr R: arithmetic shift right register by 3. Ans:

(a) 00011000. (b) 00011101. (c) 00011000. Overflow (d) 11110100

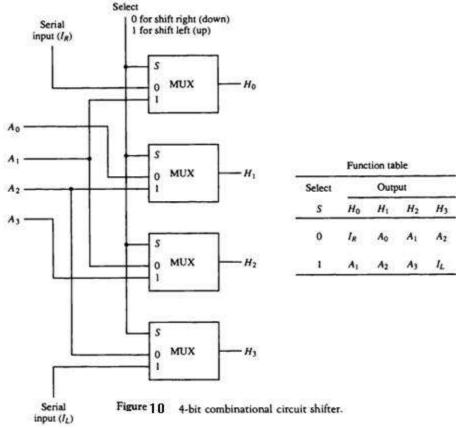

A combinational circuit shifter can be constructed with multiplexers as shown in Fig (10). The 4-bit shifter has four data inputs,  $A_0$  through  $A_3$ , and four data outputs,  $H_0$  through  $H_3$ . There are two serial inputs, one for shift left (I<sub>L</sub>) and the other for shift right (I<sub>R</sub>).

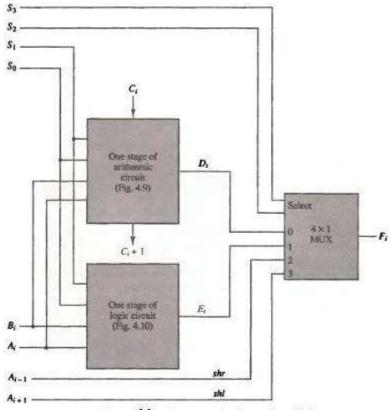

### Arithmetic Logic Shift Unit

Computer systems employ a number of storage registers connected to a common operational unit called an arithmetic logic unit, abbreviated ALU. The arithmetic, logic, and shift circuits introduced in previous sections can be combined into one ALU with common selection variables. One stage of an arithmetic logic shift unit is shown in Fig (11) with the functional table(8):

Figure 11 One stage of arithmetic logic shift unit.

|                                         | Operation select |                |    |     |                            |                      |

|-----------------------------------------|------------------|----------------|----|-----|----------------------------|----------------------|

| S,                                      | S2               | S <sub>1</sub> | So | Cin | Operation                  | Function             |

| 0                                       | 0                | 0              | 0  | 0   | F = A                      | Transfer A           |

| 0                                       | 0                | 0              | 0  | 1   | F = A + 1                  | Increment A          |

| 0                                       | 0                | 0              | 1  | 0   | F = A + B                  | Addition             |

| 0                                       | 0                | 0              | 1  | 1   | F = A + B + 1              | Add with carry       |

| 0                                       | 0                | 1              | 0  | 0   | $F = A + \overline{B}$     | Subtract with borrow |

| 000000000000000000000000000000000000000 | 0                | 1              | 0  | 1   | $F = A + \overline{B} + 1$ | Subtraction          |

| 0                                       | 0                | 1              | 1  | 0   | F = A - 1                  | Decrement A          |

| 0                                       | 0                | 1              | 1  | 1   | F = A                      | Transfer A           |

| 0                                       | 1                | 0              | 0  | ×   | $F = A \wedge B$           | AND                  |

| 0                                       | 1                | 0              | 1  | ×   | $F = A \lor B$             | OR                   |

| 0                                       | 1                | 1              | 0  | ×   | $F = A \oplus B$           | XOR                  |

| 0                                       | 1                | 1              | 1  | ×   | $F = \overline{A}$         | Complement A         |

| 1                                       | 0                | x              | ×  | ×   | $F = \operatorname{shr} A$ | Shift right A into F |

| 1                                       | 1                | ×              | ×  | ×   | $F = \operatorname{shl} A$ | Shift left A into F  |

TABLE 8 Function Table for Arithmetic Logic Shift Unit

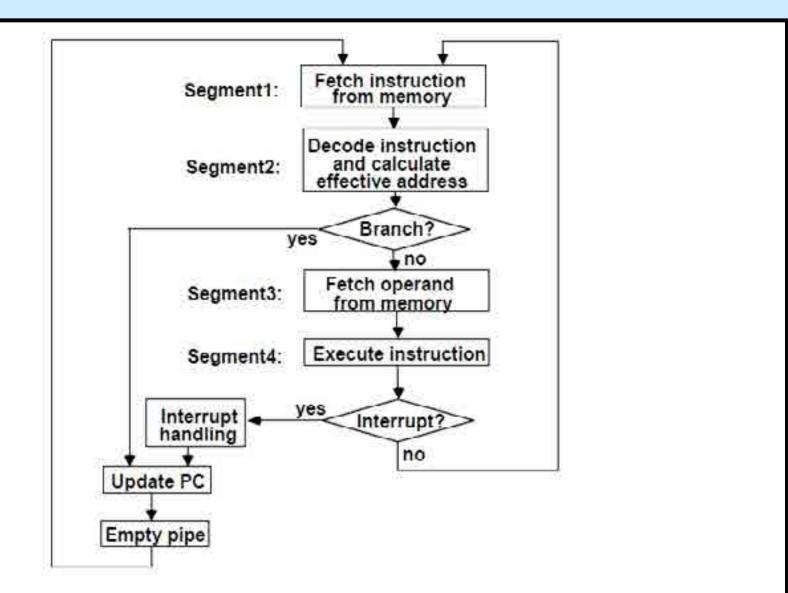

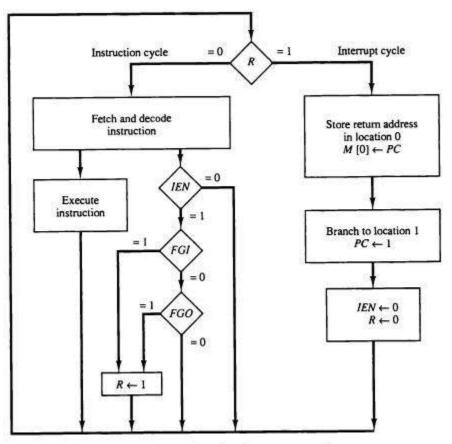

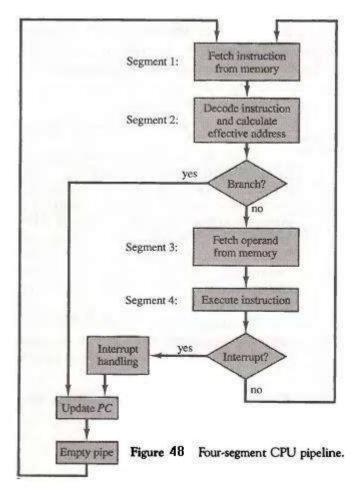

The way that the interrupt is handled by the computer can be explained by means of the flowchart of Fig(19). An interrupt flip-flop R is included in the computer.

Figure 19 Flowchart for interrupt cycle.

# **Design of Basic Computer**

The basic computer consists of the following hardware components:

- 1. A memory unit with 4096 words of 16 bits each

- 2. Nine registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC

- 3. Seven flip-flops: I, S, E, R, IEN, FGI, and FGO

- 4. Two decoders: a 3 x 8 operation decoder and a 4 x 16 timing decoder

- 5. A 16-bit common bus

- 6. Control logic gates

- 7. Adder and logic circuit connected to the input of AC The outputs of the control logic circuit are:

- 1. Signals to control the inputs of the nine registers

- 2. Signals to control the read and write inputs of memory

- 3. Signals to set, clear, or complement the flip-flops

- 4. Signals for  $S_2$ ,  $S_1$ , and  $S_0$  to select a register for the bus

- 5. Signals to control the AC adder and logic circuit.

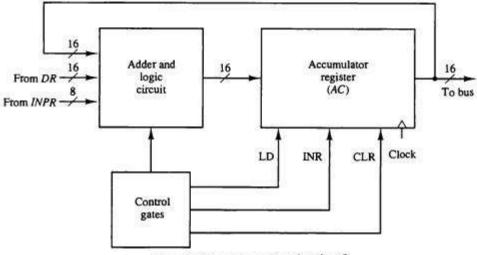

# Design of Accumulator Logic

The circuits associated with the AC register are shown in Fig(20). The adder and logic circuit has three sets of inputs.

Figure 20 Circuits associated with AC.

In order to design the logic associated with AC, it is necessary to go over the register transfer statements and extract all the statements that change the content of AC.

| $AC \leftarrow AC \land DR$                         | AND with DR        |

|-----------------------------------------------------|--------------------|

| $AC \leftarrow AC + DR$                             | Add with DR        |

| $AC \leftarrow DR$                                  | Transfer from DR   |

| $AC(0-7) \leftarrow INPR$                           | Transfer from INPR |

| $AC \leftarrow \overline{AC}$                       | Complement         |

| $AC \leftarrow \text{shr } AC, AC(15) \leftarrow E$ | Shift right        |

| $AC \leftarrow shl AC, AC(0) \leftarrow E$          | Shift left         |

| AC←0                                                | Clear              |

| $AC \leftarrow AC + 1$                              | Increment          |

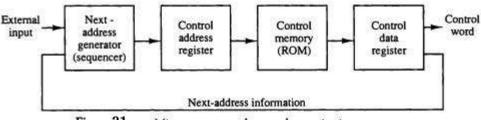

# Control Memory

The function of the control unit in a digital computer is to initiate sequences of microoperations. The number of different types of microoperations that are available in a given system is finite. A control unit whose binary control variables are stored in memory is called a microprogrammed control unit. Each word in control memory contains within it a microinstruction. The microinstruction specifies one or more microoperations for the system. A sequence of microinstructions constitutes a microprogram.

A computer that employs a microprogrammed control unit will have two separate memories: a main memory and a control memory. The main memory is available to the user for storing the programs. The contents of main memory may alter when the data are manipulated and every time that the program is changed. The user's program in main memory consists of machine

instructions and data. While the control memory holds a fixed microprogram that cannot be altered by the occasional user.

The general configuration of a microprogrammed control unit is demonstrated in the block diagram of Fig(21).

Figure 21 Microprogrammed control organization.

# **Address Sequencing**

Microinstructions are stored in control memory in groups, with each group routine specifying a routine. An initial address is loaded into the control address register when power is turned on in the computer. This address is usually the address of the first microinstruction that activates the instruction fetch routine. The fetch routine may be sequenced by incrementing the control address register through the rest of its microinstructions.

In summary, the address sequencing capabilities required in a control memory are:

- 1. Incrementing of the control address register.

- 2. Unconditional branch or conditional branch, depending on status bit conditions.

- 3. A mapping process from the bits of the instruction to an address for control memory.

- 4. A facility for subroutine call and return.

# **Instruction format:**

The computer instruction format is depicted in Fig(22-a). It consists of three fields: a 1bit held for indirect addressing symbolized by J, a 4-bit operation code (opcode), and an 11bit address field. Fig(22-b) lists four of the 16 possible memory-reference instructions.

| 15       | 14     | 11 10       | . 0                                        |

|----------|--------|-------------|--------------------------------------------|

| I        | Opcode |             | Address                                    |

|          |        | (a) Instruc | tion format                                |

| Sy       | mbol   | Opcode      | Description                                |

| ADD      |        | 0000        | $AC \leftarrow AC + M [EA]$                |

| BRANCH   |        | 0001        | If $(AC < 0)$ then $(PC \leftarrow EA)$    |

| STORE    |        | 0010        | $M[EA] \leftarrow AC$                      |

| EXCHANGE |        | 0011        | $AC \leftarrow M[EA], M[EA] \leftarrow AC$ |

EA is the effective address

(b) Four computer instructions

Figure 22 Computer instructions.

### Microinstruction Format

The microinstruction format for the control memory is shown in Fig(23). The format 20 bits of the microiristruction are divided into four functional parts. The three fields Fl, F2, and F3 specify microoperations for the computer. The CD field selects status bit conditions. The BR field specifies the type of branch to be used. The AD field contains a branch address. The address field is seven bits wide, since the control memory has  $128 = 2^7$  words.

The microoperations are subdivided into three fields of three bits each. The three bits in each field are encoded to specify seven distinct microoperations as listed in Table (13). This gives a total of 21 microoperations.

The CD (condition) field consists of two bits which are encoded to specify four status bit conditions as listed in Table. The first condition is always a 1, so that a reference to CD = 00 (or the symbol U) will always find the condition to be true. When this condition is used in conjunction with the BR (branch) field, it provides an unconditional branch operation. The indirect bit I is available from bit 15 of DR after an instruction is read from memory. The sign bit of AC provides the next status bit.

| 3     | 3         | 3          | 2                         | 2  | 7     |

|-------|-----------|------------|---------------------------|----|-------|

| Fl    | F2        | F3         | CD                        | BR | AD    |

| F1, F | 2, F3: Mi |            | tion fields<br>or branchi |    | 0.000 |

|       |           | anch field |                           |    |       |

AD: Address field

Figure 23 Microinstruction code format (20 bits).

| TABLE | 13  | Symbols and Binary Code for Microinstruction Fields |  |

|-------|-----|-----------------------------------------------------|--|

| INDLL | 1.3 | Symbols and binary Code for Micromstruction rieus   |  |

| F1  | Microoperation           | Symbol | F2  | Microoperation              | Symbol | F3  | Microoperation                | Symbol |

|-----|--------------------------|--------|-----|-----------------------------|--------|-----|-------------------------------|--------|

| 000 | None                     | NOP    | 000 | None                        | NOP    | 000 | None                          | NOP    |

| 001 | $AC \leftarrow AC + DR$  | ADD    | 001 | $AC \leftarrow AC - DR$     | SUB    | 001 | $AC \leftarrow AC \oplus DR$  | XOR    |

| 010 | AC ← 0                   | CLRAC  | 010 | $AC \leftarrow AC \lor DR$  | OR     | 010 | $AC \leftarrow \overline{AC}$ | COM    |

| 011 | $AC \leftarrow AC + 1$   | INCAC  | 011 | $AC \leftarrow AC \land DR$ | AND    | 011 | AC ← shl AC                   | SHL    |

| 100 | $AC \leftarrow DR$       | DRTAC  | 100 | $DR \leftarrow M[AR]$       | READ   | 100 | $AC \leftarrow shr AC$        | SHR    |

| 101 | $AR \leftarrow DR(0-10)$ | DRTAR  | 101 | DR ← AC                     | ACTDR  | 101 | $PC \leftarrow PC + 1$        | INCPC  |

| 110 | $AR \leftarrow PC$       | PCTAR  | 110 | $DR \leftarrow DR + 1$      | INCDR  | 110 | $PC \leftarrow AR$            | ARTPC  |

| 111 | $M[AR] \leftarrow DR$    | WRITE  | 111 | $DR(0-10) \leftarrow PC$    | PCTDR  | 111 | Reserved                      |        |

|    |              |        |                      | BR | Symbol          | Function                                                        |

|----|--------------|--------|----------------------|----|-----------------|-----------------------------------------------------------------|

| CD | Condition    | Symbol | Comments             | 00 | JMP             | $CAR \leftarrow AD$ if condition = 1                            |

| CD | Condition    | Symbol | comments             |    |                 | $CAR \leftarrow CAR + 1$ if condition = 0                       |

| 00 | Always $= 1$ | U      | Unconditional branch | 01 | CALL            | $CAR \leftarrow AD$ , $SBR \leftarrow CAR + 1$ if condition = 1 |

| 01 | DR(15)       | I      | Indirect address bit |    |                 | $CAR \leftarrow CAR + 1$ if condition = 0                       |

| 10 | AC(15)       | S      | Sign bit of AC       | 10 | RET             | $CAR \leftarrow SBR$ (Return from subroutine)                   |

| 11 | AC = 0       | z      | Zero value in AC     | 11 | MAP             | $CAR(2-5) \leftarrow DR(11-14), CAR(0,1,6) \leftarrow 0$        |

|    |              |        |                      |    | A ST CONTRACTOR |                                                                 |

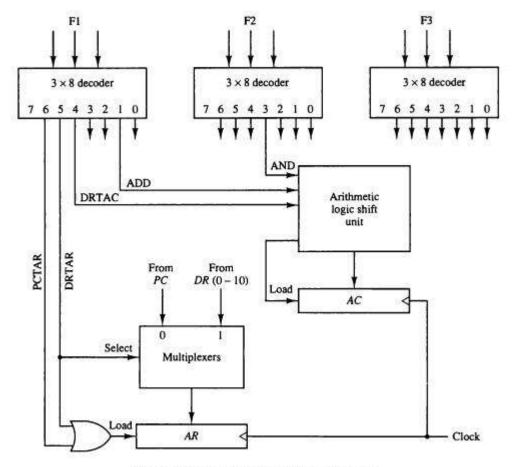

# **Design of Control Unit**

The Fig(24) shows the three decoders and some of the connections that must be made from their outputs. Each of the three fields of the microinstruction presently available in the output of control memory are decoded with a 3x8 decoder to provide eight outputs. For example, when FI = 101 (binary 5), the next clock pulse transition transfers the content of DK(0-10) to AR (symbolized by DRTAR in Table). Similarly, when FI = 110 (binary 6) there is a transfer from PC to AR (symbolized by PCTAR).

Figure 24 Decoding of microoperation fields.

# **Central Processing Unit**

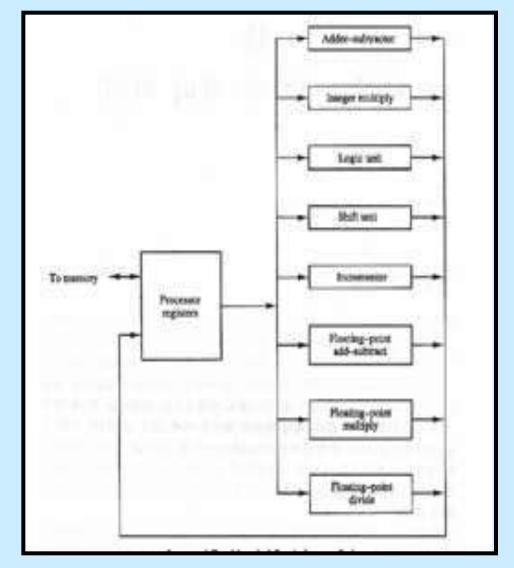

The CPU is made up of three major parts, as shown in Fig(25).

- 1- The register set stores intermediate data used during the execution of the instructions. The arithmetic

- 2- logic unit (ALU) performs the required microoperations for executing the instructions.

- 3- The control unit supervises the transfer of information among the registers and instructs the ALU as to which operation to perform.

Figure 25 Major components of CPU.

# **General Register Organization**

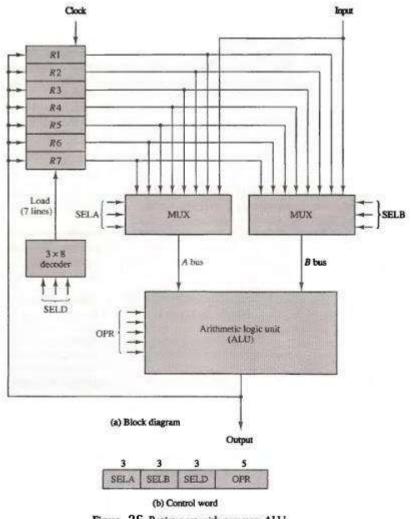

The memory locations are needed for storing pointers, counters, return addresses, temporary results, and partial products during multiplication. A bus organization for seven CPU registers is shown in Fig(26):

Figure 26 Register set with common ALU.

The control unit that operates the CPU bus system directs the information flow through the registers and ALU by selecting the various components in the system. For example, to perform the operation: The control must provide binary selection variables to the following selector inputs:

- 1. MUX A selector (SELA): to place the content of R2 into bus A.

- 2. MUX B selector (SELB): to place the content of R3 into bus B.

- 3. ALU operation selector (OPR): to provide the arithmetic addition A + B.

- 4. Decoder destination selector (SELD): to transfer the content of the output bus into Rl. To achieve a fast response time, the ALU is constructed with high-speed circuits.

There are 14 binary selection inputs in the unit, and their combined value control word specifies a control word. The three bits of SELA select a source register for the A input of the ALU. The three bits of SELB select a register for the B input of the ALU. The three bits of SELD select a destination register using the decoder and its seven load outputs. The five bits of OPR select one of the operations in the ALU.

The encoding of the register selections is specified in Table(14):

| Binary<br>Code | SELA  | SELB  | SELD |

|----------------|-------|-------|------|

| 000            | Input | Input | None |

| 001            | Ř1    | Ř1    | R1   |

| 010            | R2    | R2    | R2   |

| 011            | R3    | R3    | R3   |

| 100            | R4    | R4    | R4   |

| 101            | R5    | R5    | R5   |

| 110            | R6    | R6    | R6   |

| 111            | R7    | R7    | R7   |

TABLE 14 Encoding of Register Selection Fields

Table(15) OPR field has five bits and each operation is designated with a symbolic name.

| TABLE 15 | Encoding of ALU Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | The state of the s |

| OPR    |                |        |

|--------|----------------|--------|

| Select | Operation      | Symbol |

| 00000  | Transfer A     | TSFA   |

| 00001  | Increment A    | INCA   |

| 00010  | Add $A + B$    | ADD    |

| 00101  | Subtract A - B | SUB    |

| 00110  | Decrement A    | DECA   |

| 01000  | AND A and B    | AND    |

| 01010  | OR A and B     | OR     |

| 01100  | XOR A and B    | XOR    |

| 01110  | Complement A   | COMA   |

| 10000  | Shift right A  | SHRA   |

| 11000  | Shift left A   | SHLA   |

For example, the subtract microoperation given by the statement:

$R1 \leftarrow R2 - R3$

The binary control word for the subtract microoperation is 010 011 001 00101 and is obtained as follows:

| Field:        | SELA | SELB | SELD | OPR   |

|---------------|------|------|------|-------|

| Symbol:       | R2   | R3   | R1   | SUB   |

| Control word: | 010  | 011  | 001  | 00101 |

### **Stack Organization**

A useful feature that is included in the CPU of most computers is a stack or last-in, firstout (LIFO) list. The two operations of a stack are the insertion and deletion of items. The operation of insertion is called push, while the operation of deletion is called pop. In a 64-word stack, the stack pointer contains 6 bits because  $2^6 = 64$ .

The push operation is implemented with the following sequence of microoperations:

| $SP \leftarrow SP + 1$                   | Increment stack pointer        |

|------------------------------------------|--------------------------------|

| $M[SP] \leftarrow DR$                    | Write item on top of the stack |

| If $(SP = 0)$ then $(FULL \leftarrow 1)$ | Check if stack is full         |

| EMTY ←0                                  | Mark the stack not empty       |

The pop operation consists of the following sequence of microoperations:

| $DR \leftarrow M[SP]$                    | Read item from the top of stack |

|------------------------------------------|---------------------------------|

| $SP \leftarrow SP - 1$                   | Decrement stack pointer         |

| If $(SP = 0)$ then $(EMTY \leftarrow 1)$ | Check if stack is empty         |

| FULL ←0                                  | Mark the stack not full         |

### **Instruction Formats**

The format of an instruction is usually depicted in a rectangular box symbolizing the bits of the instruction as they appear in memory words or in a control register. The bits of the instruction are divided into groups called fields. The most common fields found in instruction formats are:

- 1. An operation code field that specifies the operation to be performed.

- 2. An address field that designates a memory address or a processor register.

- 3. A mode field that specifies the way the operand or the effective address is determined. An example of an accumulator-type organization, the instruction that specifies an arithmetic addition is defined by an assembly language instruction as:

| Addressing<br>Mode | Effective<br>Address | Content<br>of AC |  |  |

|--------------------|----------------------|------------------|--|--|

| Direct address     | 500                  | 800              |  |  |

| Immediate operand  | 201                  | 500              |  |  |

| Indirect address   | 800                  | 300              |  |  |

| Relative address   | 702                  | 325              |  |  |

| Indexed address    | 600                  | 900              |  |  |

| Register           |                      | 400              |  |  |

| Register indirect  | 400                  | 700              |  |  |

| Autoincrement      | 400                  | 700              |  |  |

| Autodecrement      | 399                  | 450              |  |  |

TABLE 16 Tabular List of Numerical Example

### **Data Transfer and Manipulation**

Most computer instructions can be classified into three categories:

- 1. Data transfer instructions.

- 2. Data manipulation instructions.

- 3. Program control instructions.

*Data transfer instructions* cause transfer of data from one location to another without changing the binary information content. The table(17) list the Data transfer instructions:

| Name     | Mnemonic |

|----------|----------|

| Load     | LD       |

| Store    | ST       |

| Move     | MOV      |

| Exchange | XCH      |

| Input    | IN       |

| Output   | OUT      |

| Push     | PUSH     |

| Pop      | POP      |

TABLE 17 Typical Data Transfer Instructions

*Data manipulation instructions* are those that perform arithmetic, logic, and shift operations. The data manipulation instructions in a typical computer are usually divided into three basic types:

- 1- Arithmetic instructions.

- 2. Logical and bit manipulation instructions.

- 3. Shift instructions.

# Computer Architecture Part2 Asst. Prof. Dr. Raheem Abdul Sahib 2023-2024

### **Reduced Instruction Set Computer (RISC)**

:

An important aspect of computer architecture is the design of the instruction set for the processor. The instruction set chosen for a particular computer determines the way that machine language programs are constructed. A computer with a large number of instructions is classified as a Complex Instruction Set Computer, abbreviated CISC. In the early 1980s, a number of computer designers recommended that computers use fewer instructions with simple constructs so they can be executed much faster within the CPU without having to use memory as often.

The RISC (Reduced Instruction Set Computer) type of computer is classified as a reduced instruction set computer or RISC.

### In Summary, The Major Characteristics of CISC Architecture Are:

- 1. A large number of instructions—typically from 100 to 250 instructions.

- 2. Some instructions that perform specialized tasks and are used infrequently.

- 3. A large variety of addressing modes—typically from 5 to 20 different modes.

- 4. Variable-length instruction formats.

- 5. Instructions that manipulate operands in memory.

### The Major Characteristics of A RISC Processor Are:

- 1. Relatively few instructions.

- 2. Relatively few addressing modes.

- 3. Memory access limited to load and store instructions.

- 4. All operations done within the registers of the CPU.

- 5. Fixed-length, easily decoded instruction format.

- 6. Single-cycle instruction execution.

- 7. Hardwired rather than microprogrammed control.

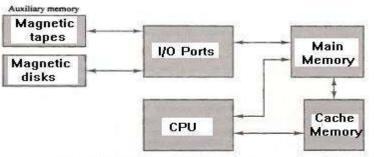

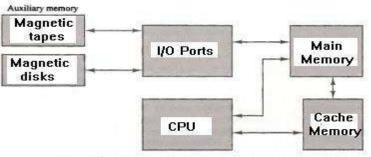

#### Memory Hierarchy

The memory unit is an essential component in any digital computer since it is needed for storing programs and data. The memory unit that communicates directly with the CPU is called the main memory. Devices that provide backup storage are called auxiliary memory. They are used for storing system programs, large data files, and other backup information. Only programs and data currently needed by the processor reside in main memory. All other information is stored in auxiliary memory and transferred to main memory when needed. A special very-highspeed memory called a cache is sometimes used to increase the speed of processing by making current programs and data available to the CPU at a rapid rate. Fig(29) shows the Memory Hierarchy:

Figure 29 Memory hierarchy in a computer system.

*Main Memory* The main memory is the central storage unit in a computer system. It is a relatively large and fast memory used to store programs and data during the computer operation. The principal technology used for the main memory is based on semiconductor integrated circuits. Integrated circuit RAM chips are available in two possible operating modes: